Антивирусные программы и технологии

Антивирусы— сканеры вирусов.

Вирусы имеют некие механизмы видоизменения. Эти механизмы называются

мутационными механизмами.

Другими словами, вирусы побитно меняют информацию, последовательность выполнения операций. Если в таком случае будет производиться проверка на вирусы, то изменившийся мутационный вирус будет незамеченным.

Способы распознавания вирусов:

1)

поиск вирусов (сканирование) по программам компенсатора и декомпенсатора:

Но разработчики вирусов добавляют шифратор и дешифратор:

2)

проверка целостности работы:

Суть в том, что для каждого файла специальным образом, который знает только ОС, рассчитывается контрольная сумма.

Благодаря специальному файлу, который хранится в засекреченном месте и в котором находятся все контрольные суммы, производится сравнение, позволяющее понять, заражена ли программа.

3)

проверка поведения:

Существует ряд параметров, которым процесс должен удовлетворять. Если процесс начинает вести себя подозрительно, то он блокируется, а затем выдаётся сообщение, что что-то не так.

Хорошие антивирусные программы совмещают все эти три подхода.Правила, которые следует соблюдать:

- Использовать ОС, которые предоставляют необходимый уровень безопасности

- Нужно устанавливать лицензионное программное обеспечение

- Нужно пользоваться надёжными лицензионными антивирусными программами

- Необходимо создавать резервные копии

При работе с мобильными программами (интернетом) существует 2 принципиальных вида программ:

- апплет— некая мобильная программа, связанная с интерактивной справочной системой

- агент— программа, которая запускается пользователем для выполнения каких-либо действий

Для безопасной работы программы ОС применяют различные свойства и приёмы:

1)

«Песочница»

Для программы выделяется определённое место, в котором она может работать.

2)

Интерпретация

Программы апплетов или агентов компилируются в некий машинный язык (например, Java). После этого вместо программы работает её интерпретатор. Таким образом осуществляется проверка каждой команды перед исполнением.

9 Многопроцессорные системы

9.1 Последовательные и параллельные архитектуры ЭВМ

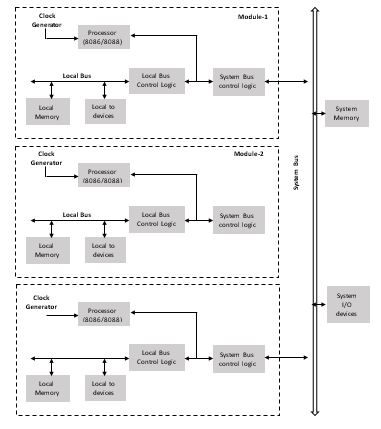

Многопроцессорные системы — вычислительные системы, использующие для обработки данных более одного процессора.

Примеры:

Двухпроцессорные ПК, мощные серверы с множеством процессоров, суперкомпьютеры

Преимущества:

— большие инженерные и исследовательские приложения, выполняемые на суперкомпьютерах, обеспечивают прирост производительности за счёт параллельной обработки данных на нескольких процессорах

-коммерческие и научные организации используют многопроцессорные системы для повышения производительности, представления задачам достаточных ресурсов и достижения высокой производительности, предоставления задачам достаточных ресурсов и достижения высокой надёжности

ОС многопроцессорных ЭВМ должны дополнительно гарантировать, что:

— все процессоры загружены работой

— процессы равномерно распределены в системе

— выполнение взаимосвязанных процессов синхронизировано

— процессы работают с постоянными копиями данных, хранящихся в общей памяти

— обеспечивается взаимное исключение для выхода из тупиковых ситуаций

Классификация многопроцессорных систем:

— по структуре каналов обработки данных

— по схеме соединений процессоров

— по способу распределения ресурсов между процессорами

— по разделению функций ОС между процессорами

— по способу работы с памятью

Классификация многопроцессорных систем:

— по структуре каналов обработки данных

— по схеме соединения процессоров

— по способу распределения ресурсов между процессорами

— по разделению функций ОС между процессорами

— по способу работы с памятью

Поток — битовая последовательность данных или инструкций, передаваемых процессоруБитовый поток – логический объект, описывающий последовательность независимо выполняемых программных инструкций внутри процесса.

Архитектуры компьютеров можно классифицировать по структуре каналов обработки данных, основываясь на понятии потоков данных и команд.

Классификация последовательных и параллельных архитектур ЭВМ:

—

SISD (Single Instruction, Single Data)— архитектура компьютеров, в которой один процессор последовательно выполняет инструкцию за инструкцией из потока команд над элементами данных (к этой архитектуре относятся традиционные одноядерные однопроцессорные компьютеры)

—

MISD (Multiple Instruction stream, Single Data stream) – архитектура компьютеров, содержащих несколько вычислительных элементов, выполняющих независимые параллельные потоки операций над одним потоком данных (к этой архитектуре относятся многоядерные процессоры)

—

SIMD (Single instruction, Multiple data)— архитектура компьютеров, состоящих из нескольких процессорных элементов, одновременно выполняющих одни и те же инструкции над различными элементами данных (к этой архитектуре относят векторные и матричные процессоры)

—

MIMD (Multiple Instruction stream, Multiple Data stream)— архитектура компьютеров, состоящая из множества полноценных процессоров, каждый из которых выполняет свою последовательность инструкций над своим потоком данных (это полноценная параллельная архитектура настоящих многопроцессорных систем)

Векторный процессор – разновидность SIMD-компьютера, в котором используется один одноядерный процессор, одновременно выполняющий одну и ту же инструкцию над несколькими элементами данных. Матричный процессор— SIMD- система, состоящая из множества простых процессоров, каждый из которых выполняет такое же действие, как и остальные процессоры системы, но над своим элементом данных.

В системах SISD и SIMD не могут выполняться параллельно несколько вычислительных потоков. Однако потоки выполняемые в MISD- системах работают с одними и теми же данными и поэтому не являются независимыми. Параллелизм в полной мере свойственен только MIMD.

Для повышения производительности процессоров в SISD- системах используется конвейерная обработка данных и суперскалярная архитектура. Это позволяет одновременно выполнять инструкции нескольких команд.

Замечание:

Архитектура ЭВМ Джона фон Неймана является последовательной SISD архитектурой с одним потоком данных и одним потоком команд.

10. Ввод-вывод

Важнейшая функция ОС — управление всеми устройствами ввода-вывода (перехват сообщений, обеспечение интерфейса)

Большой диапазон скоростей (интернет, диски- 100Мб, мышь- 100 кб)

Ввод- вывод:— механическая часть — электронная часть (процессор-контроллер, адаптер)

Они поставляют интерфейс, подчиняются функциональным стандартам для того, чтобы устройство было совместимо с большинством ОС.

Интерфейс может управляться контроллером. Устройством и процессом является интерфейс низкого уровня.

У каждого контроллера есть

несколько регистров, с помощью которых можно обратиться к центральному процессору.

У каждого устройства есть

буфер данных, куда записывается информация.

Существует 2 альтернативных способа реализации доступа к управлению регистром:

—

каждому регистру присваивается номер

IN REG PORT

OUT REG PORT

— прямой доступ к памяти— доступ прямого отображения на адресное пространство

POP- 11

10.1 Принципы программного ввода-вывода

- Независимость ввода-вывода от устройств

- Принципы единообразного именования

- Принцип обработки ошибок

- Синхронный (блокирующий)

- Асинхронный

Буферизация— процесс, когда информация скачивается в буфер, а оттуда перемещается туда, куда надо.Выделенные устройства— устройства коллективного доступа.

10.2 Способы ввода-вывода

1)Программный ввод-вывод:

Например, хотим напечатать страницу.

Посылается запрос на доступ к устройству: «Можем напечатать или нет?» -> (да)

->страница помещается в пространство ядра -> запрос: «Готов ли принтер?» -> (да) -> в буфер памяти принтера -> печать

2)Управляемый прерываниями ввод-вывод:

На печать одного символа выделяется 10 мс.

Первый символ на печать — Процессор прерывается — Следующий символ на печать — Процессор прерывается

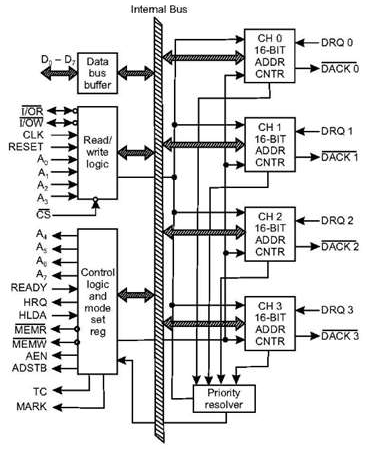

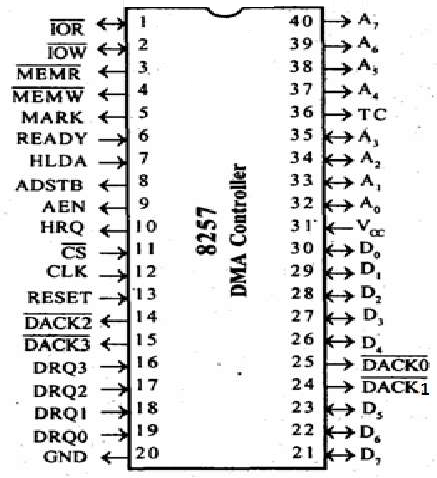

3)Ввод-вывод с прямым доступом к памяти

В машину вмонтирован специальный контроллер- DMA (direct memory allocation). Прерывания не доходят до центрального процессора, а скорость контроллера уменьшается.

10.3 Программные уровни ввода-вывода

1)Обработчик прерываний (либо обрабатывает прерывания, либо блокирует драйвер)

Если не обработалось прерывание, то происходит:

— запоминание текущего состояния процесса

— сохранение содержимого всех регистров

— контекст процесса

— запоминание содержимого стека

— выдача подтверждения контроллеру прерываний

— копирование содержимого регистров с того места, где произошло прерывание, в таблицу процессов

— запуск процедуры обработки прерываний

— выбор процесса, которому передаётся управление

— установка контекста другого процесса

— загрузка регистров нового процесса

— передача управления следующему процессу

2)Драйверы устройств

Драйвер- программа для управления устройства ввода-вывода, подключённого к компьютеру.

Замечания:

- пишется производителем устройств

- подчиняется международным стандартам

- могут управлять несколькими устройствами.

Устройство подключается к ОС через программы- драйверы

Процессоры миллионов компьютеров по всему миру знают только одно — непрерывно выполнять инструкции. А что такое инструкция? Читай дальше что бы узнать.

Что такое инструкция?

Инструкция — это минимальная единица программы, которая сообщает ЦП что делать с помощью серии инструкций, которые выполняются последовательно. Каждая инструкция представляет собой количество битов в двоичном коде, который разделен на три разные части:

- Биты инструкций: эти биты указывают, какую инструкцию будет выполнять ЦП, и поэтому путь, по которому инструкция будет следовать для выполнения, также называется кодом операции.

- Биты адресации: указывают, по какому адресу памяти хранятся данные.

- Биты режима: биты режима указывают, как выполняется инструкция, они используются, когда есть несколько способов выполнить инструкцию или есть разные условия.

Если вы хотите узнать, как процессор выполняет инструкции, мы рекомендуем статью » Вот как ваш процессор выполняет инструкции, которые дает ему программное обеспечение ”В HardZone, на том же сайте.

Инструкции по адресации

В зависимости от того, где находятся данные, у нас могут быть разные варианты одного и того же типа инструкций, способ, которым процессор получает доступ к данным, называется режимом адресации.

- Немедленная адресация используется, когда данные представляют собой одну и ту же инструкцию, в этом случае данные хранятся в регистре или внутренней памяти процессора, которые будут выполняться оттуда.

- Второй тип адресации — прямая, когда программа указывает адрес памяти, в котором находятся данные.

- Третий тип адресации — косвенный, который дает нам адрес, по которому находится адрес памяти, в котором находятся данные.

Следует уточнить, что некоторые инструкции не имеют режима адресации, поскольку они не требуют данных для выполнения.

Типы инструкций в ЦП

Вот краткое изложение наиболее распространенных инструкций, используемых различными процессорами. Эти инструкции являются общими для всех регистров и наборов инструкций, независимо от того, являются ли они x86, ARM, MIPS, PowerPC и так далее. Также не имеет значения, является ли набор инструкций RISC или CISC.

- Арифметические манипуляции инструкции — это те, которые выполняют операции математической обработки, такие как сложение, вычитание, умножение и деление. А также более сложные операции, такие как тригонометрические формулы, квадратные корни, степени.

- Наблюдения и советы этой статьи мы подготовили на основании опыта команды логические инструкции — это второй тип инструкций, выполняемых ALU, на самом деле они представляют собой двоичные операции, имитирующие работу логических вентилей. То есть AND, OR, XOR, NAND, NOR, XNOR и NOT.

- Инструкции по манипулированию битами основаны на манипулировании битами идемной строки с помощью таких инструкций, как сдвиг бита влево или вправо, изменение порядка или их переключение.

- Инструкции по перемещению данных отвечает за перемещение данных из одной части памяти в другую, из одной памяти в другую, из процессора в память и из памяти в процессор.

- Инструкции по управлению программой те, которые активируются при выполнении определенных условий, таких как

- Наблюдения и советы этой статьи мы подготовили на основании опыта команды инструкции по переходу — это те, которые указывают, что программа переходит не к следующему адресу памяти, а к конкретному адресу памяти, который отмечен инструкцией перехода.

Типы данных и множественность инструкций

Потому что сегодня ЦП может работать с разными типами данных, например с целыми числами и с плавающей запятой. Некоторые арифметические инструкции часто дублируются для набора команд с плавающей запятой. Существуют также векторные инструкции, такие как наборы инструкций AVX или также известные как инструкции SIMD, которые работают с несколькими операндами одновременно.

Поскольку эти инструкции выполняются в разных единицах, они в конечном итоге требуют разных битов инструкций, а это означает, что добавление новых типов данных в процессор означает во многих случаях значительное увеличение набора инструкций, их сложности. . а также часть, которая декодирует и выполняет их на ЦП.

Эта статья про единицу информации. Для использования в других целях, см Бит (значения) .

Бит является самым основным единица информации в компьютерных и цифровых коммуникаций . Название это сокращение от двоичной цифры . Бит представляет логическое состояние с одним из двух возможных значений . Эти значения обычно представлены как «

1 » или « 0 » , но обычно используются другие представления, такие как истина / ложь , да / нет , + / — или вкл / выкл .

Соответствие между этими значениями и физическими состояниями нижележащего хранилища или устройства является условием, и разные назначения могут использоваться даже в пределах одного и того же устройства или программы . Это может быть физически реализовано с помощью устройства с двумя состояниями.

Символом двоичной цифры является либо «бит» согласно рекомендации стандарта IEC 80000-13 : 2008, либо символ нижнего регистра «b», как рекомендовано стандартом IEEE 1541-2002 .

Непрерывная группа двоичных цифр обычно называется битовой строкой , битовым вектором или одномерным (или многомерным) битовым массивом . Группа из восьми двоичных цифр называется одним байтом , но исторически размер байта строго не определен. Часто половинные, полные, двойные и четверные слова состоят из числа байтов, которое является малой степенью двойки.

В теории информации , один бит является информационная энтропия из двоичной случайной величины , что равно 0 или 1 с равной вероятностью, или информации , которая достигается , когда значение такой переменной становится известным. Как единица информации бит также известен как шеннон , названный в честь Клода Э. Шеннона .

История

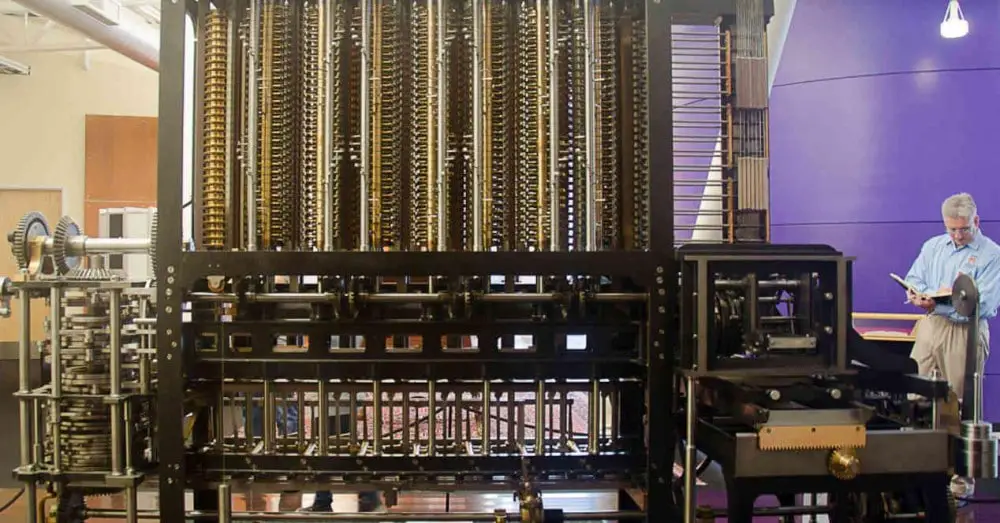

Кодирование данных дискретными битами использовалось в перфокартах, изобретенных Базилем Бушоном и Жан-Батистом Соколом (1732 г.), разработанных Жозефом Мари Жаккардом (1804 г.), а затем принятых Семеном Корсаковым , Чарльзом Бэббиджем , Германом Холлеритом и ранними производители компьютеров, такие как IBM . Вариантом этой идеи была перфорированная бумажная лента . Во всех этих системах носитель (карта или лента) концептуально содержал множество позиций отверстий; каждая позиция могла быть либо перфорирована, либо нет, таким образом неся один бит информации. Битовое кодирование текста также использовалось в азбуке Морзе (1844 г.) и ранних машинах цифровой связи, таких как телетайпы и биржевые тикеры (1870 г.).

Ральф Хартли предложил использовать логарифмическую меру информации в 1928 году. Клод Э. Шеннон впервые использовал слово «бит» в своей основополагающей статье 1948 года « Математическая теория коммуникации ». Он приписал его происхождение Джону У. Тьюки , который 9 января 1947 года написал меморандум Bell Labs, в котором он сократил «двоичную информационную цифру» до просто «бит». Ванневар Буш написал в 1936 году «биты информации», которые можно было хранить на перфокартах, используемых в механических компьютерах того времени. Первый программируемый компьютер, построенный Конрадом Цузе , использовал двоичную запись чисел.

Физическое представление

Бит может быть сохранен цифровым устройством или другой физической системой, которая существует в любом из двух возможных различных состояний . Это могут быть два стабильных состояния триггера, два положения электрического переключателя , два различных уровня напряжения или тока, разрешенные схемой , два различных уровня интенсивности света , два направления намагничивания или поляризации , ориентация обратимого двойного скрученная ДНК и т. д.

Биты могут быть реализованы в нескольких формах. В большинстве современных вычислительных устройств бит обычно представлен импульсом электрического напряжения или тока или электрическим состоянием триггерной схемы.

Для устройств, использующих положительную логику , цифровое значение 1 (или логическое значение true) представлено более положительным напряжением по сравнению с представлением 0 . Конкретные напряжения различаются для разных семейств логики, и допускаются вариации, чтобы учесть старение компонентов и помехоустойчивость. Например, в транзисторно-транзисторной логике (ТТЛ) и совместимых схемах цифровые значения 0 и 1 на выходе устройства представлены не более 0,4 В и не менее 2,6 В соответственно; в то время как входы TTL предназначены для распознавания 0,8 В или ниже как 0 и 2,2 В или выше как 1 .

Передача и обработка

Биты передаются по одному при последовательной передаче и несколькими битами при параллельной передаче . Операция побитового необязательно обрабатывает биты по одному за раз. Скорость передачи данных обычно измеряется в десятичных единицах СИ, кратных единице бит в секунду (бит / с), например кбит / с.

Место хранения

В самых ранних неэлектронных устройствах обработки информации, таких как ткацкий станок Жаккарда или аналитическая машина Бэббиджа , бит часто сохранялся как положение механического рычага или шестерни или наличие или отсутствие отверстия в определенной точке бумажной карты. или ленту . Первые электрические устройства для дискретной логики (такие как схемы управления лифтами и светофорами , телефонные переключатели и компьютер Конрада Цузе) представляли биты как состояния электрических реле, которые могли быть либо «разомкнутыми», либо «замкнутыми». Когда реле были заменены электронными лампами , начиная с 1940-х годов, производители компьютеров экспериментировали с различными методами хранения, такими как импульсы давления, идущие по ртутной линии задержки , заряды, хранящиеся на внутренней поверхности электронно-лучевой трубки , или непрозрачные пятна. напечатанные на стеклянных дисках по фотолитографии техники.

В 1950-х и 1960-х годах эти методы были в значительной степени вытеснены устройствами магнитного хранения, такими как память с магнитным сердечником , магнитные ленты , барабаны и диски , где бит был представлен полярностью намагничивания определенной области ферромагнитной пленки или изменение полярности с одного направления на другое. Тот же принцип позже был использован в магнитной пузырьковой памяти, разработанной в 1980-х годах, и до сих пор используется в различных предметах с магнитной полосой , таких как билеты на метро и некоторые кредитные карты .

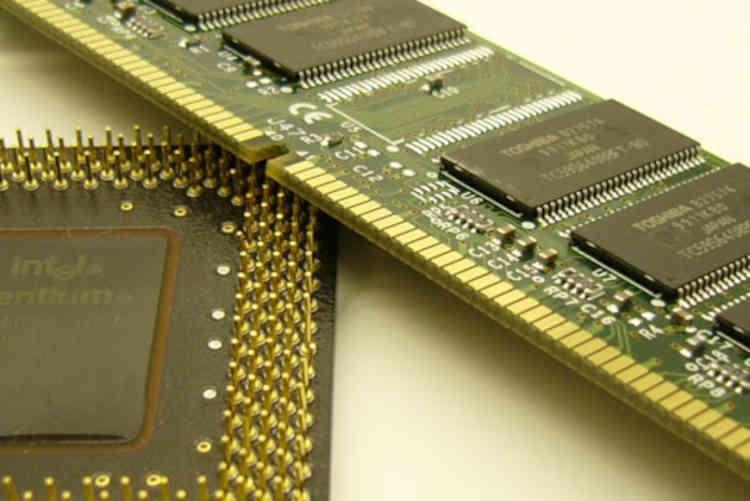

В современной полупроводниковой памяти , такой как динамическая память с произвольным доступом , два значения бита могут быть представлены двумя уровнями электрического заряда, хранящегося в конденсаторе . В некоторых типах программируемых логических массивов и постоянной памяти бит может быть представлен наличием или отсутствием проводящего пути в определенной точке схемы. В оптических дисках бит кодируется как наличие или отсутствие микроскопической ямки на отражающей поверхности. В одномерных штрих-кодах биты кодируются как толщина чередующихся черных и белых линий.

Единица и символ

Бит не определен в Международной системе единиц (СИ). Однако Международная электротехническая комиссия выпустила стандарт IEC 60027 , в котором указано, что символ двоичной цифры должен быть «бит», и его следует использовать во всех кратных, таких как «кбит», для килобита. Однако строчная буква «b» также широко используется и была рекомендована стандартом IEEE 1541 (2002) . Напротив, заглавная буква «B» является стандартным и обычным символом для байта.

|

Многобитовые блоки

|

||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

|

|

|||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

| Порядки величины данных |

Несколько бит

Множественные биты могут быть выражены и представлены несколькими способами. Для удобства представления часто повторяющихся групп битов в информационных технологиях традиционно использовалось несколько единиц информации . Наиболее распространенным является единичный байт , введенный Вернером Бухгольцем в июне 1956 года, который исторически использовался для представления группы битов, используемых для кодирования одного символа текста (до тех пор, пока многобайтовая кодировка UTF-8 не взяла верх) в компьютере, и для этого причина, по которой он использовался в качестве основного адресуемого элемента во многих компьютерных архитектурах . Тенденция в проектировании оборудования сошлась на наиболее распространенной реализации использования восьми бит на байт, как это широко используется сегодня. Однако из-за двусмысленности, связанной с базовым дизайном аппаратного обеспечения, единичный октет был определен для явного обозначения последовательности из восьми битов.

Компьютеры обычно обрабатывают биты группами фиксированного размера, обычно называемыми « словами ». Как и в случае с байтом, количество битов в слове также зависит от конструкции оборудования и обычно составляет от 8 до 80 бит или даже больше в некоторых специализированных компьютерах. В 21 веке у розничных персональных или серверных компьютеров размер слова составляет 32 или 64 бита.

Международная система единиц определяет ряд десятичных префиксов для кратных стандартизированных единиц , которые обычно используются также с битом и байтом. Префиксы кило (10 3 ) — йотта (10 24 ) увеличиваются на величину , кратную одной тысяче, и соответствующие единицы — это килобит (кбит) через йоттабит (юбит).

Информационная емкость и сжатие информации

Когда информационная емкость системы хранения или канала связи представлена в битах или битах в секунду , это часто относится к двоичным цифрам, которые представляют собой аппаратную способность компьютера хранить двоичные данные ( 0 или 1 , вверх или вниз, текущее или нет. , так далее.). Информационная емкость системы хранения — это только верхняя граница количества хранимой в ней информации. Если два возможных значения одного бита памяти не равновероятны, этот бит памяти содержит менее одного бита информации. Если значение полностью предсказуемо, то считывание этого значения не дает никакой информации (нулевые энтропийные биты, поскольку нет разрешения неопределенности и, следовательно, информация недоступна). Если компьютерный файл, который использует n битов памяти, содержит только m < n битов информации, то эта информация в принципе может быть закодирована примерно m битами, по крайней мере, в среднем. Этот принцип лежит в основе технологии сжатия данных. По аналогии, двоичные цифры оборудования относятся к объему доступного пространства для хранения (например, количество ведер, доступных для хранения вещей), и к информационному содержанию заполнения, которое имеет разные уровни детализации (мелкая или грубая, т. Е. сжатая или несжатая информация). Когда детализация более мелкая — когда информация более сжатая, — в том же ведре может содержаться больше.

Например, по оценкам, совокупные технологические возможности мира для хранения информации обеспечивают 1300 эксабайт аппаратных цифр. Однако, когда это пространство хранения заполнено и соответствующее содержимое оптимально сжато, это составляет всего 295 эксабайт информации. При оптимальном сжатии результирующая пропускная способность приближается к информации Шеннона или информационной энтропии .

Битовые вычисления

Некоторые побитовые инструкции компьютерного процессора (такие как набор битов ) работают на уровне манипулирования битами, а не данными, интерпретируемыми как совокупность битов.

В 1980-х годах, когда растровые компьютерные дисплеи стали популярными, некоторые компьютеры предоставляли специальные инструкции по передаче битовых блоков для установки или копирования битов, соответствующих заданной прямоугольной области на экране.

В большинстве компьютеров и языков программирования, когда упоминается бит в группе битов, такой как байт или слово, он обычно определяется числом от 0 и выше, соответствующим его положению в байте или слове. Однако, 0 может относиться либо к большей или меньшей мере значащий бит в зависимости от контекста.

Прочие информационные блоки

Подобно крутящему моменту и энергии в физике; теоретико-информационная информация размера и хранение данных имеют одинаковую размерность в единицах измерения , но в общем случае нет смысла для сложения, вычитания или иным образом комбинируя единицы математически, хотя один может действовать как ограничение на другом.

Единицы информации, используемые в теории информации, включают шеннон (Sh), естественную единицу информации (nat) и хартли (Hart). Один шеннон — это максимальное ожидаемое значение информации, необходимой для определения состояния одного бита хранилища. Они связаны соотношением 1 Sh ≈ 0,693 nat ≈ 0,301 Hart.

Некоторые авторы также определяют двоичный разряд как произвольную информационную единицу, эквивалентную некоторому фиксированному, но неуказанному количеству битов.

Смотрите также

- Байт

- Целое число (информатика)

- Примитивный тип данных

- Трит (тройная цифра)

- Кубит (квантовый бит)

- Bitstream

- Энтропия (теория информации)

- Битрейт и скорость передачи

- Двоичная система счисления

- Троичная система счисления

- Шеннон (единица)

использованная литература

внешние ссылки

- Битовый калькулятор — инструмент, обеспечивающий преобразование между битами, байтами, килобитами, килобайтами, мегабитами, мегабайтами, гигабитами, гигабайтами.

- BitXByteConverter — инструмент для вычисления размеров файлов, емкости хранилища и цифровой информации в различных единицах

Что такое микропроцессоры, сегодня знает каждый. Это одно из самых интересных технологических новшеств в электронике после появления транзистора в 1948 году. Чудо-устройства не только начали революцию в области цифровой электроники, но и проникли почти во все сферы жизни человека. Они применяются в сложнейших управляющих контроллерах, оборудовании диспетчерского управления, в простых игровых автоматах и даже игрушках.

- Что такое микропроцессоры?

- Принцип действия

- Шины

- Арифметико-логическое устройство и внутренние регистры

- Декодер, блок управления и память

- Интерфейс

- Передача информации

- Интерфейсные устройства

- Языки программирования

- Набор команд микрокомпьютера

- Память микропроцессора

- Инструкции микропроцессора

- Работа микропроцессора на примере вычисления факториала

- Декодирование

Что такое микропроцессоры?

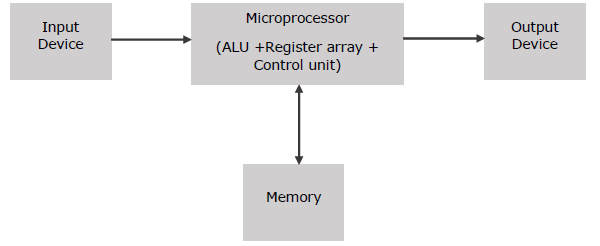

Компьютер, большой и не очень, функционально (в упрощенной форме) может быть представлен в виде блок-схемы, состоящей из трех основных частей:

- Центрального процессорного устройства (ЦПУ), которое выполняет необходимые логические и арифметические операции, используя регистры (память микропроцессора), и контролирует синхронизацию и общую работу всей системы.

- Устройств ввода-вывода, которые служат для подачи данных в ЦПУ (к ним относятся коммутаторы, аналого-цифровые преобразователи, устройства чтения карт памяти, клавиатура, накопители на жестких дисках и т. д.) и вывода результатов вычислений (светодиоды, дисплеи, цифроаналоговые преобразователи, принтеры, плоттеры, линии связи и т. д.). Так подсистема ввода-вывода позволяет компьютеру общаться с внешним миром. Такие устройства также называются периферийными.

- Памяти, в которой хранятся команды (программа) и данные. Обычно состоит из ОЗУ (памяти с произвольным доступом) и ПЗУ (постоянной, предназначенной только для чтения).

Микропроцессор является интегральной схемой, предназначенной для работы в качестве ЦПУ микрокомпьютера.

Принцип действия

Назначение микропроцессора заключается в считывании каждой команды из памяти, ее декодировании и выполнении.

ЦПУ обрабатывает данные согласно инструкциям программы в форме логических и арифметических операций. Информация извлекается из памяти или поступает из устройства ввода, и результат обработки сохраняется в памяти или доставляется на соответствующее устройство вывода так, как это указано в командах. Вот что такое микропроцессоры. Для выполнения всех указанных функций у них имеются различные функциональные блоки.

Такая внутренняя или организационная структура ЦПУ, определяющая его работу, называется его архитектурой.

Типичная схема устройства микропроцессора представлена ниже.

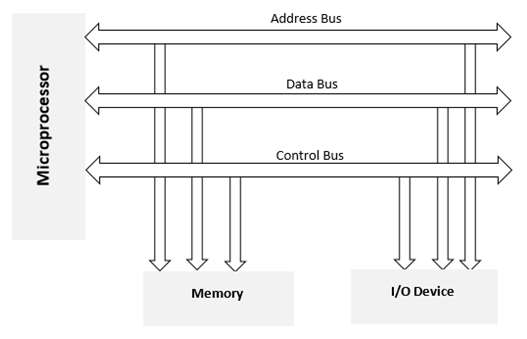

Шины

Микрокомпьютер оперирует двоичным кодом. Бинарная информация представлена двоичными цифрами, называемыми битами. Группа битов образует машинное слово (их количество зависит от конкретной реализации). Обычные размеры слова равны 4, 8, 12, 16, 32 и 64 бит. Байт и полубайт представляют собой набор из 8 и 4 бит соответственно.

Шины соединяют различные блоки устройства и позволяют им обмениваться машинными словами. Они выполнены в виде отдельного провода для каждого бита, что позволяет обмениваться всеми разрядами машинного слова одновременно. Обработка информации в ЦПУ также происходит параллельно. Таким образом, шины могут рассматриваться как магистрали передачи данных. Их ширина определяется количеством составляющих их сигнальных линий. По адресной шине ЦПУ передает адрес устройства ввода-вывода или ячейки памяти, к которой он хочет получить доступ. Этот адрес принимается всеми устройствами, подключенными к процессору. Но реагирует на него только то, которому был адресован запрос. Шина данных служит для отправки и приема информации из устройств ввода-вывода и памяти, в т. ч. команд. Очевидно, что она является двунаправленной, а адресная – однонаправленной. Шина управления используется для передачи и приема сигналов управления между микропроцессором и различными элементами системы.

Арифметико-логическое устройство и внутренние регистры

Представляет собой комбинационную сеть, которая выполняет логические и арифметические операции над данными.

В состав микропроцессора обычно входит и ряд регистров. Они используются для временного хранения команд, данных и адресов во время выполнения программы. Например, у микропроцессора Intel 8085 имеется 8-битный аккумулятор (Acc), 6 8-битных регистров общего назначения (B, C, D, E, H и L), 8-разрядный регистр команд (IR), в котором хранится следующая исполняемая инструкция, 16-битный программный счетчик с адресом следующей команды, которую необходимо выбрать из памяти в IR, 16-битный указатель стека, регистр флагов, который сигнализирует о выполнении определенных условий, возникающих во время выполнения логических и арифметических операций, и некоторые другие специальные регистры для внутренних процессов, доступа к которым у программиста нет.

Декодер, блок управления и память

Расшифровывает каждую команду и управляет внешними и внутренними блоками, обеспечивая правильную логическую работу системы.

Для сохранения команд, данных и результатов вычислений требуется наличие полупроводниковых запоминающих устройств. Программа записывается в память, подключенную к микропроцессору через адресную шину и шины данных и управления (подобно устройствам ввода-вывода).

Интерфейс

Если к ЦПУ необходимо подключить одно или несколько устройств ввода-вывода, то возникает необходимость в соответствующем интерфейсе. Он выполняет следующие 4 функции:

- буферизацию, необходимую для обеспечения совместимости микропроцессора и периферии;

- декодирование адреса для выбора одного из нескольких подключенных к системе ввода-вывода устройств;

- декодирование команд, требуемое для выполнения функций, отличных от передачи данных;

- синхронизацию и управление всеми вышеперечисленными функциями.

Передача информации

Обмен данными, который происходит между периферийным устройством и микрокомпьютером, относятся либо к их программной передаче, либо к прямому доступу к памяти.

В первом случае загруженная программа запрашивает систему ввода-вывода на передачу данных микропроцессору или из него. Как правило, информация поступает в аккумулятор, хотя другие внутренние регистры могут также участвовать. Программная передача обычно используется при пересылке небольшого объема данных относительно медленными устройствами ввода-вывода, например, периферийным умножителем, периферийным АЛУ и т. д. В таких случаях трансфер обычно производится пословно.

Прямой доступ к памяти или захват циклов контролируется периферийным устройством. При этом системой ввода-вывода принудительно задерживает работа микропроцессора, пока пересылка не будет завершена. Поскольку процесс контролируется аппаратно, интерфейс сложнее, чем требуется для программной передачи данных. Используется при необходимости переслать большой блок информации, например, из таких периферийных хранилищ, как гибкие диски и высокоскоростной картридер.

Интерфейсные устройства

Для разработки пользовательских интерфейсов доступно обширное аппаратное обеспечение. К нему относятся мультиплексоры и демультиплексоры, линейные драйверы и приемники, буферы, стабильные и моностабильные мультивибраторы, триггер-защелки, вентильные схемы, сдвиговые регистры и т. д. Есть и более сложные программируемые интерфейсы, функции которых можно изменить командой микропроцессора. Эти интерфейсы могут быть общего или специального назначения.

Языки программирования

Поскольку компьютер может хранить и обрабатывать информацию в двоичной форме, команды для подачи на машину должны быть представлены в двоичном формате. В таком виде программа является машинным языком.

На языке ассемблера команды, включая места хранения, представлены буквенно-цифровыми символами, называемыми мнемоническими. По сравнению с машинным языком их использование значительно облегчает написание программ. Однако если программа написана на таком мнемоническом языке, она должна быть переведена в инструкции, понятные машине, чтобы их можно было хранить и выполнять в микрокомпьютере. В основном одна команда ассемблера транслируется в одну команду машинного языка.

Писать программы на ассемблере очень утомительно и требует много времени. Поэтому широкое распространение получили языки высокого уровня, такие как Fortran, Cobol, Algol, Pascal, которые можно затем перевести на язык машины. В этом случае одному оператору обычно соответствует несколько инструкций машинного языка.

Набор команд микрокомпьютера

Основные характеристики микропроцессора также определяются набором инструкций.

Обычно он состоит из 5 групп:

- Группа передачи данных. Данные команды помогают перемещать информацию между регистрами внутри микропроцессора, между памятью и регистром или ячейками памяти.

- Арифметическая группа позволяет складывать, вычитать, увеличивать или уменьшать данные в памяти или регистрах (например, сложить содержимое двух регистров ЦПУ).

- Логическая группа используется для операций И, ИЛИ, ИСКЛЮЧАЮЩЕГО ИЛИ, сравнения, циклического сдвига, дополнения данных в памяти или регистрах (например, чтобы пропустить через схему ИЛИ содержимое двух регистров микропроцессора).

- Группа ветвления включает безусловные и условные переходы, вызов подпрограмм и возвращение из них. Условные инструкции служат для того, чтобы определенная операция выполнялась только в случае выполнения определенного условия (например, если требуется перейти к конкретной команде, когда результат последнего вычисления был равен нулю). Они обеспечивают возможность программе самой принимать решения.

- Группа стека, ввода-вывода и управления микропроцессором производит передачу данных между ЦПУ и периферией, манипулирует стеком и изменяет внутренние флаги управления. Эти команды позволяют программисту остановить устройство, перевести его в нерабочее состояние, включить и отключить систему прерываний и т. д.

Инструкции, которые хранятся вместе с данными в памяти, могут иметь длину в 1 или несколько байт. Длинные команды хранятся в последовательных ячейках памяти, причем адрес первого байта всегда используется как адрес всей команды. Кроме того, первый байт всегда является кодом операции.

Память микропроцессора

Знакомство с подробностями, касающимися компьютерной памяти и ее иерархии помогут лучше понять содержание этого раздела.

Выше мы писали о шинах (адресной и данных), а также о каналах чтения (RD) и записи (WR). Эти шины и каналы соединены с памятью: оперативной (ОЗУ, RAM) и постоянным запоминающим устройством (ПЗУ, ROM). В нашем примере рассматривается микропроцессор, ширина каждой из шин которого составляет 8 бит. Это значит, что он способен выполнять адресацию 256 байт (два в восьмой степени). В один момент времени он может считывать из памяти или записывать в нее 8 бит данных. Предположим, что этот простой микропроцессор располагает 128 байтами ПЗУ (начиная с адреса 0) или 128 байтами оперативной памяти (начиная с адреса 128).

Модуль постоянной памяти содержит определенный предварительно установленный постоянный набор байт. Адресная шина запрашивает у ПЗУ определенный байт, который следует передать шине данных. Когда канал чтения (RD) меняет свое состояние, модуль ПЗУ предоставляет запрошенный байт шине данных. То есть в данном случае возможно только чтение данных.

Из оперативной памяти процессор может не только считывать информацию, он способен также записывать в нее данные. В зависимости от того, чтение или запись осуществляется, сигнал поступает либо через канал чтения (RD), либо через канал записи (WR). К сожалению, оперативная память энергозависима. При отключении питания она теряет все размещенные в ней данные. По этой причине компьютеру необходимо энергонезависимое постоянное запоминающее устройство.

Более того, теоретически компьютер может обойтись и вовсе без оперативной памяти. Многие микроконтроллеры позволяют размещать необходимые байты данных непосредственно в чип процессора. Но без ПЗУ обойтись невозможно. В персональных компьютерах ПЗУ называется базовой системой ввода и вывода (БСВВ, BIOS, Basic Input/Output System). Свою работу при запуске микропроцессор начинает с выполнения команд, найденных им в BIOS.

Команды BIOS выполняют тестирование аппаратного обеспечения компьютера, а затем они обращаются к жесткому диску и выбирают загрузочный сектор. Этот загрузочный сектор является отдельной небольшой программой, которую BIOS сначала считывает с диска, а затем размещает в оперативной памяти. После этого микропроцессор начинает выполнять команды расположенного в ОЗУ загрузочного сектора. Программа загрузочного сектора сообщает микропроцессору о том, какие данные (предназначенные для последующего выполнения процессором) следует дополнительно переместить с жесткого диска в оперативную память. Именно так происходит процесс загрузки процессором операционной системы.

Инструкции микропроцессора

Даже простейший микропроцессор способен обрабатывать достаточно большой набор инструкций. Набор инструкций является своего рода шаблоном. Каждая из этих загружаемых в регистр команд инструкций имеет свое значение. Людям непросто запомнить последовательность битов, поэтому каждая инструкция описывается в виде короткого слова, каждое из которых отражает определенную команду. Эти слова составляют язык ассемблера процессора. Ассемблер переводит эти слова на понятный процессору язык двоичных кодов.

Приведем список слов-команд языка ассемблера для условного простого процессора, который мы рассматриваем в качестве примера к нашему повествованию:

- LOADA mem — Загрузить (load) регистр A из некоторого адреса памяти

- LOADB mem — Загрузить (load) регистр B из некоторого адреса памяти

- CONB con — Загрузить постоянное значение (constant value) в регистр B

- SAVEB mem — Сохранить (save) значение регистра B в памяти по определенному адресу

- SAVEC mem — Сохранить (save) значение регистра C в памяти по определенному адресу

- ADD — Сложить (add) значения регистров A и B. Результат действия сохранить в регистре C

- SUB — Вычесть (subtract) значение регистра B из значения регистра A. Результат действия сохранить в регистре C

- MUL — Перемножить (multiply) значения регистров A и B. Результат действия сохранить в регистре C

- DIV — Разделить (divide) значение регистра A на значение регистра B. Результат действия сохранить в регистре C

- COM — Сравнить (compare) значения регистров A и B. Результат передать в тестовый регистр

- JUMP addr — Перепрыгнуть (jump) к указанному адресу

- JEQ addr — Если выполняется условие равенства значений двух регистров, перепрыгнуть (jump) к указанному адресу

- JNEQ addr — Если условие равенства значений двух регистров не выполняется, перепрыгнуть (jump) к указанному адресу

- JG addr — Если значение больше, перепрыгнуть (jump) к указанному адресу

- JGE addr — Если значение больше или равно, перепрыгнуть (jump) к указанному адресу

- JL addr — Если значение меньше, перепрыгнуть (jump) к указанному адресу

- JLE addr — Если значение меньше или равно, перепрыгнуть (jump) к указанному адресу

- STOP — Остановить (stop) выполнение

Английские слова, обозначающие выполняемые действия, в скобках приведены неспроста. Так мы можем видеть, что язык ассемблера (как и многие другие языки программирования) основан на английском языке, то есть на привычном средстве общения тех людей, которые создавали цифровые технологии.

Работа микропроцессора на примере вычисления факториала

Рассмотрим работу микропроцессора на конкретном примере выполнения им простой программы, которая вычисляет факториал от числа «5». Сначала решим эту задачку «в тетради»:

факториал от 5 = 5! = 5 * 4 * 3 * 2 * 1 = 120

На языке программирования C этот фрагмент кода, выполняющего данное вычисление, будет выглядеть следующим образом:

a=1;f=1;while (a < = 5){ f = f * a; a = a + 1;}

Когда эта программа завершит свою работу, переменная f будет содержать значение факториала от пяти.

Компилятор C транслирует (то есть переводит) этот код в набор инструкций языка ассемблера. В рассматриваемом нами процессоре оперативная память начинается с адреса 128, а постоянная память (которая содержит язык ассемблера) начинается с адреса 0. Следовательно, на языке данного процессора эта программа будет выглядеть так:

// Предположим, что a по адресу 128// Предположим, что F по адресу 1290 CONB 1 // a=1;1 SAVEB 1282 CONB 1 // f=1;3 SAVEB 1294 LOADA 128 // if a > 5 the jump to 175 CONB 56 COM7 JG 178 LOADA 129 // f=f*a;9 LOADB 12810 MUL11 SAVEC 12912 LOADA 128 // a=a+1;13 CONB 114 ADD15 SAVEC 12816 JUMP 4 // loop back to if17 STOP

Теперь возникает следующий вопрос: а как же все эти команды выглядят в постоянной памяти? Каждая из этих инструкций должна быть представлена в виде двоичного числа. Чтобы упростить понимание материала, предположим, что каждая из команд языка ассемблера рассматриваемого нами процессора имеет уникальный номер:

- LOADA — 1

- LOADB — 2

- CONB — 3

- SAVEB — 4

- SAVEC mem — 5

- ADD — 6

- SUB — 7

- MUL — 8

- DIV — 9

- COM — 10

- JUMP addr — 11

- JEQ addr — 12

- JNEQ addr — 13

- JG addr — 14

- JGE addr — 15

- JL addr — 16

- JLE addr — 17

- STOP — 18

Будем считать эти порядковые номера кодами машинных команд (opcodes). Их еще называют кодами операций. При таком допущении, наша небольшая программа в постоянной памяти будет представлена в таком виде:

// Предположим, что a по адресу 128// Предположим, что F по адресу 129Addr машинная команда/значение0 3 // CONB 11 12 4 // SAVEB 1283 1284 3 // CONB 15 16 4 // SAVEB 1297 1298 1 // LOADA 1289 12810 3 // CONB 511 512 10 // COM13 14 // JG 1714 3115 1 // LOADA 12916 12917 2 // LOADB 12818 12819 8 // MUL20 5 // SAVEC 12921 12922 1 // LOADA 12823 12824 3 // CONB 125 126 6 // ADD27 5 // SAVEC 12828 12829 11 // JUMP 430 831 18 // STOP

Как вы заметили, семь строчек кода на языке C были преобразованы в 18 строчек на языке ассемблера. Они заняли в ПЗУ 32 байта.

Декодирование

Понравилась статья? Расскажите друзьям:

Оцените статью, для нас это очень важно:

Проголосовавших: 6 чел.

Средний рейтинг: 5 из 5.

Микропроцессор – Обзор

Микропроцессор – это управляющий блок микрокомпьютера, изготовленный на небольшом чипе, способный выполнять операции ALU (Арифметическая логическая единица) и связываться с другими подключенными к нему устройствами.

Микропроцессор состоит из ALU, массива регистров и блока управления. АЛУ выполняет арифметические и логические операции с данными, полученными из памяти или устройства ввода. Массив регистров состоит из регистров, обозначенных буквами, как B, C, D, E, H, L и аккумулятора. Блок управления контролирует поток данных и инструкций внутри компьютера.

Блок-схема базового микрокомпьютера

Как работает микропроцессор?

Микропроцессор следует последовательности: выборка, декодирование, а затем выполнение.

Первоначально инструкции хранятся в памяти в последовательном порядке. Микропроцессор извлекает эти инструкции из памяти, затем декодирует их и выполняет эти инструкции до тех пор, пока не будет достигнута команда STOP. Позже он отправляет результат в двоичном формате на выходной порт. Между этими процессами регистр временно хранит данные, а ALU выполняет вычислительные функции.

Список терминов, используемых в микропроцессоре

Вот список некоторых часто используемых терминов в микропроцессоре:

-

Набор инструкций – это набор инструкций, которые может понять микропроцессор.

-

Полоса пропускания – это число битов, обрабатываемых в одной инструкции.

-

Тактовая частота – определяет количество операций в секунду, которые может выполнять процессор. Он выражается в мегагерцах (МГц) или гигагерцах (ГГц). Он также известен как тактовая частота.

-

Длина слова – зависит от ширины внутренней шины данных, регистров, ALU и т. Д. 8-разрядный микропроцессор может одновременно обрабатывать 8-разрядные данные. Длина слова варьируется от 4 до 64 бит в зависимости от типа микрокомпьютера.

-

Типы данных – Микропроцессор имеет несколько форматов типов данных, таких как двоичные, BCD, ASCII, числа со знаком и без знака.

Набор инструкций – это набор инструкций, которые может понять микропроцессор.

Полоса пропускания – это число битов, обрабатываемых в одной инструкции.

Тактовая частота – определяет количество операций в секунду, которые может выполнять процессор. Он выражается в мегагерцах (МГц) или гигагерцах (ГГц). Он также известен как тактовая частота.

Длина слова – зависит от ширины внутренней шины данных, регистров, ALU и т. Д. 8-разрядный микропроцессор может одновременно обрабатывать 8-разрядные данные. Длина слова варьируется от 4 до 64 бит в зависимости от типа микрокомпьютера.

Типы данных – Микропроцессор имеет несколько форматов типов данных, таких как двоичные, BCD, ASCII, числа со знаком и без знака.

Особенности микропроцессора

Вот список некоторых из самых выдающихся особенностей любого микропроцессора –

-

Экономически эффективный – микропроцессорные чипы доступны по низким ценам и, как следствие, имеют низкую стоимость.

-

Размер – микропроцессор имеет небольшой размер чипа, поэтому является портативным.

-

Низкое энергопотребление – Микропроцессоры изготавливаются с использованием металлооксидной полупроводниковой технологии, которая имеет низкое энергопотребление.

-

Универсальность – микропроцессоры универсальны, поскольку мы можем использовать один и тот же чип в ряде приложений, конфигурируя программное обеспечение.

-

Надежность – частота отказов IC в микропроцессорах очень низка, поэтому она надежна.

Экономически эффективный – микропроцессорные чипы доступны по низким ценам и, как следствие, имеют низкую стоимость.

Размер – микропроцессор имеет небольшой размер чипа, поэтому является портативным.

Низкое энергопотребление – Микропроцессоры изготавливаются с использованием металлооксидной полупроводниковой технологии, которая имеет низкое энергопотребление.

Универсальность – микропроцессоры универсальны, поскольку мы можем использовать один и тот же чип в ряде приложений, конфигурируя программное обеспечение.

Надежность – частота отказов IC в микропроцессорах очень низка, поэтому она надежна.

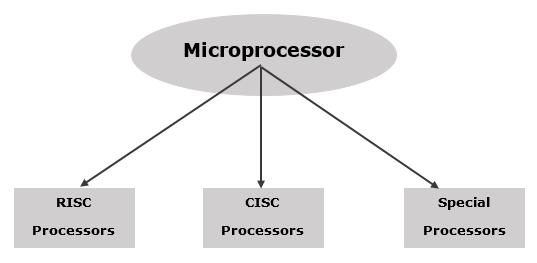

Микропроцессор – Классификация

Микропроцессор можно разделить на три категории –

RISC-процессор

RISC расшифровывается как компьютер с сокращенным набором команд . Он предназначен для сокращения времени выполнения за счет упрощения набора команд компьютера. Используя процессоры RISC, каждая инструкция требует только одного такта для выполнения результатов в единое время выполнения. Это снижает эффективность, так как появляется больше строк кода, поэтому для хранения инструкций требуется больше оперативной памяти. Компилятор также должен работать больше, чтобы преобразовать инструкции языка высокого уровня в машинный код.

Некоторые из процессоров RISC –

- Мощность ПК: 601, 604, 615, 620

- DEC Alpha: 210642, 211066, 21068, 21164

- MIPS: TS (R10000) RISC-процессор

- PA-RISC: HP 7100LC

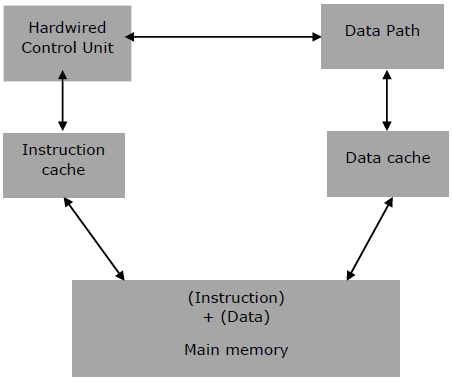

Архитектура РИСК

Микропроцессорная архитектура RISC использует высокооптимизированный набор инструкций. Он используется в портативных устройствах, таких как Apple iPod, благодаря своей энергоэффективности.

Характеристики РИСК

Основные характеристики процессора RISC следующие:

-

Он состоит из простых инструкций.

-

Он поддерживает различные форматы типов данных.

-

Он использует простые режимы адресации и инструкции фиксированной длины для конвейерной обработки.

-

Он поддерживает регистр для использования в любом контексте.

-

Время выполнения одного цикла.

-

Инструкции «LOAD» и «STORE» используются для доступа к ячейке памяти.

-

Он состоит из большего количества регистров.

-

Он состоит из меньшего количества транзисторов.

Он состоит из простых инструкций.

Он поддерживает различные форматы типов данных.

Он использует простые режимы адресации и инструкции фиксированной длины для конвейерной обработки.

Он поддерживает регистр для использования в любом контексте.

Время выполнения одного цикла.

Инструкции «LOAD» и «STORE» используются для доступа к ячейке памяти.

Он состоит из большего количества регистров.

Он состоит из меньшего количества транзисторов.

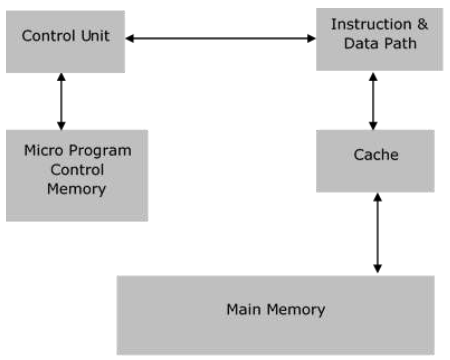

CISC Процессор

CISC расшифровывается как комплексная компьютерная инструкция . Он предназначен для минимизации количества инструкций на программу, игнорируя количество циклов на инструкцию. Акцент делается на построение сложных инструкций непосредственно в аппаратном обеспечении.

Компилятору приходится выполнять очень мало работы для перевода языка высокого уровня в язык ассемблера / машинный код, поскольку длина кода относительно мала, поэтому для хранения инструкций требуется очень мало ОЗУ.

Некоторые из процессоров CISC –

- IBM 370/168

- VAX 11/780

- Intel 80486

Архитектура CISC

Его архитектура предназначена для уменьшения стоимости памяти, поскольку в больших программах требуется больше места для хранения, что приводит к увеличению стоимости памяти. Чтобы решить эту проблему, количество команд на программу может быть уменьшено путем вложения количества операций в одну инструкцию.

Характеристики CISC

- Разнообразие режимов адресации.

- Большое количество инструкций.

- Переменная длина форматов команд.

- Для выполнения одной инструкции может потребоваться несколько циклов.

- Логика декодирования инструкций сложна.

- Для поддержки нескольких режимов адресации требуется одна инструкция.

Специальные процессоры

Это процессоры, которые предназначены для некоторых специальных целей. Немногие из специальных процессоров кратко обсуждаются –

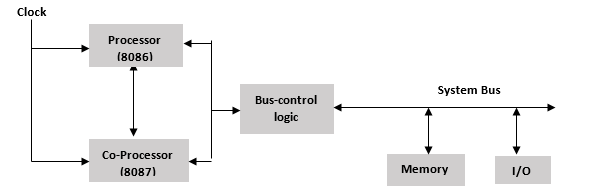

сопроцессор

Сопроцессор – это специально разработанный микропроцессор, который может выполнять свои функции во много раз быстрее, чем обычный микропроцессор.

Например – Математический сопроцессор.

Некоторые математические сопроцессоры Intel –

- 8087-используется с 8086

- 80287-используется с 80286

- 80387-используется с 80386

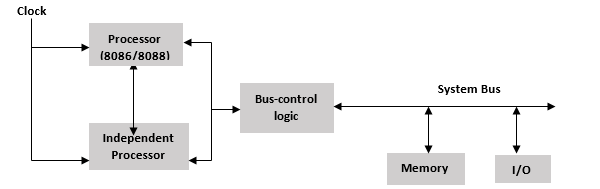

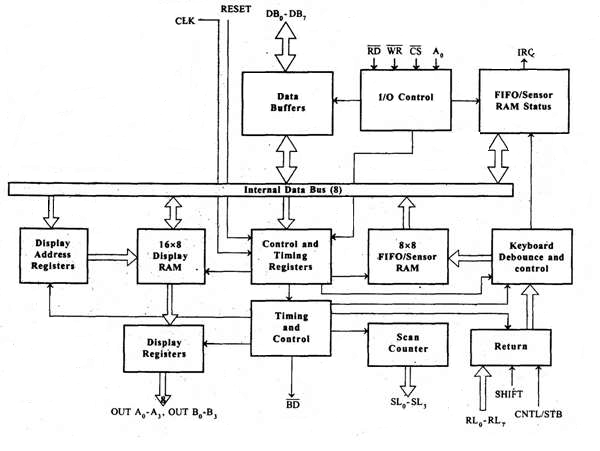

Процессор ввода / вывода

Это специально разработанный микропроцессор с собственной локальной памятью, который используется для управления устройствами ввода-вывода с минимальным участием ЦП.

Например –

- Контроллер прямого доступа к памяти

- Контроллер клавиатуры / мыши

- Контроллер графического дисплея

- Контроллер порта SCSI

Транспутер (Транзистор Компьютер)

Транспьютер – это специально разработанный микропроцессор с собственной локальной памятью и связями для соединения одного транспортера с другим транспортом для межпроцессорной связи. Впервые он был разработан в 1980 году компанией Inmos и нацелен на использование технологии СБИС.

Транспортер может использоваться как однопроцессорная система или может быть подключен к внешним каналам, что снижает стоимость строительства и повышает производительность.

Например – 16-битный T212, 32-битный T425, процессоры с плавающей запятой (T800, T805 и T9000).

DSP (цифровой сигнальный процессор)

Этот процессор специально разработан для обработки аналоговых сигналов в цифровом виде. Это делается путем выборки уровня напряжения через регулярные промежутки времени и преобразования напряжения в этот момент в цифровую форму. Этот процесс выполняется схемой, называемой аналого-цифровой преобразователь, аналого-цифровой преобразователь или АЦП.

DSP содержит следующие компоненты –

-

Память программ – хранит программы, которые DSP будет использовать для обработки данных.

-

Память данных – хранит информацию для обработки.

-

Compute Engine – выполняет математическую обработку, получая доступ к программе из памяти программ и данным из памяти данных.

-

Ввод / вывод – он подключается к внешнему миру.

Память программ – хранит программы, которые DSP будет использовать для обработки данных.

Память данных – хранит информацию для обработки.

Compute Engine – выполняет математическую обработку, получая доступ к программе из памяти программ и данным из памяти данных.

Ввод / вывод – он подключается к внешнему миру.

Его приложения –

- Синтез звука и музыки

- Аудио и видео компрессия

- Обработка видеосигнала

- 2D и 3D графическое ускорение.

Например – серия TMS 320 от Texas Instrument, например, TMS 320C40, TMS320C50.

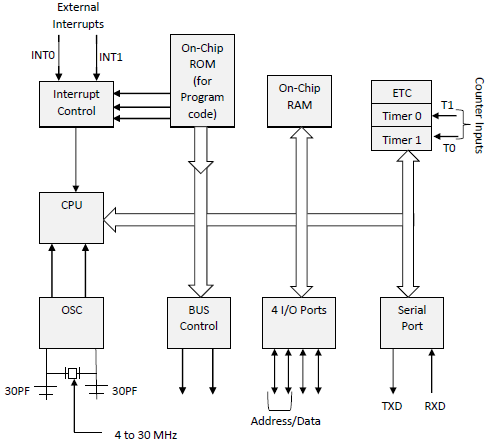

Микропроцессор – 8085 Архитектура

8085 произносится как «восемьдесят восемьдесят пять» микропроцессор. Это 8-битный микропроцессор, разработанный Intel в 1977 году с использованием технологии NMOS.

Он имеет следующую конфигурацию –

- 8-битная шина данных

- 16-битная адресная шина, которая может адресовать до 64 КБ

- 16-битный программный счетчик

- 16-битный указатель стека

- Шесть 8-битных регистров, расположенных попарно: BC, DE, HL

- Требуется питание + 5 В для работы на однофазных тактовых частотах 3,2 МГц

Используется в стиральных машинах, микроволновых печах, мобильных телефонах и т. Д.

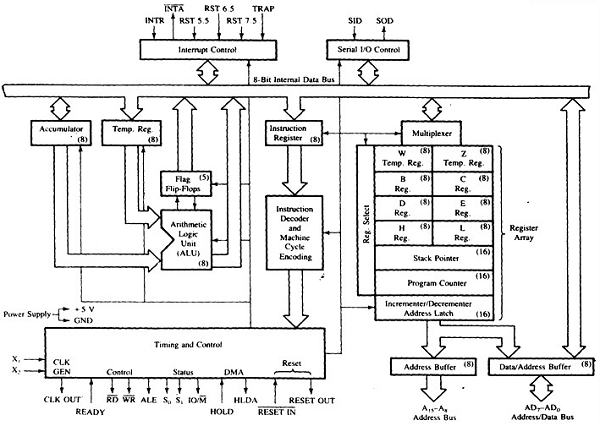

Микропроцессор 8085 – Функциональные блоки

8085 состоит из следующих функциональных блоков –

аккумуляторный

Это 8-битный регистр, используемый для выполнения арифметических, логических операций ввода-вывода и загрузки / сохранения. Он подключен к внутренней шине данных и ALU.

Арифметико-логическое устройство

Как следует из названия, он выполняет арифметические и логические операции, такие как сложение, вычитание, AND, OR и т. Д. Над 8-битными данными.

Регистр общего назначения

В процессоре 8085 имеется 6 регистров общего назначения, то есть B, C, D, E, H & L. Каждый регистр может содержать 8-битные данные.

Эти регистры могут работать в паре для хранения 16-битных данных, и их комбинация сочетания похожа на BC, DE & HL.

Счетчик команд

Это 16-битный регистр, используемый для хранения адреса памяти в следующей команде, которая должна быть выполнена. Микропроцессор увеличивает программу всякий раз, когда выполняется инструкция, так что счетчик программы указывает на адрес памяти следующей инструкции, которая будет выполнена.

Указатель стека

Это также 16-битный регистр, работающий как стек, который всегда увеличивается / уменьшается на 2 во время операций push & pop.

Временный регистр

Это 8-битный регистр, который содержит временные данные арифметических и логических операций.

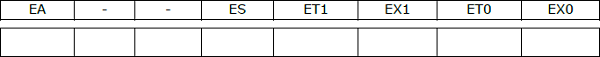

Флаг регистр

Это 8-битный регистр, имеющий пять 1-битных триггеров, которые содержат 0 или 1 в зависимости от результата, сохраненного в аккумуляторе.

Это набор из 5 шлепанцев –

- Приметы)

- Ноль (Z)

- Вспомогательный Carry (AC)

- Паритет (P)

- Нести (С)

Его битовая позиция показана в следующей таблице –

| D7 | D6 | D5 | D4 | D3 | D2 | D1 | Д0 |

|---|---|---|---|---|---|---|---|

| S | Z | переменный ток | п | CY |

Регистр команд и декодер

Это 8-битный регистр. Когда инструкция извлекается из памяти, она сохраняется в регистре команд. Декодер команд декодирует информацию, представленную в регистре команд.

Сроки и блок управления

Он обеспечивает синхронизацию и управляющий сигнал для микропроцессора для выполнения операций. Ниже приведены сигналы синхронизации и управления, которые управляют внешними и внутренними цепями.

- Управляющие сигналы: ГОТОВ, RD ‘, WR’, ALE

- Сигналы состояния: S0, S1, IO / M ‘

- Сигналы DMA: ДЕРЖАТЬ, HLDA

- Сигналы RESET: RESET IN, RESET OUT

Управление прерываниями

Как следует из названия, он контролирует прерывания во время процесса. Когда микропроцессор выполняет основную программу и всякий раз, когда происходит прерывание, микропроцессор переносит управление из основной программы для обработки входящего запроса. После завершения запроса управление возвращается к основной программе.

В микропроцессоре 8085 имеется 5 сигналов прерывания: INTR, RST 7.5, RST 6.5, RST 5.5, TRAP.

Управление последовательным вводом / выводом

Он управляет последовательной передачей данных с помощью этих двух инструкций: SID (данные последовательного ввода) и SOD (данные последовательного ввода).

Адресный буфер и адресный буфер данных

Содержимое, хранящееся в указателе стека и программном счетчике, загружается в буфер адресов и буфер данных-адресов для связи с ЦП. Микросхемы памяти и ввода / вывода подключены к этим шинам; CPU может обмениваться нужными данными с памятью и чипами ввода / вывода.

Адресная шина и шина данных

Шина данных несет данные для хранения. Он является двунаправленным, тогда как адресная шина переносит место, где она должна храниться, и является однонаправленной. Он используется для передачи данных и адреса устройств ввода-вывода.

8085 Архитектура

Мы попытались изобразить архитектуру 8085 с помощью следующего изображения –

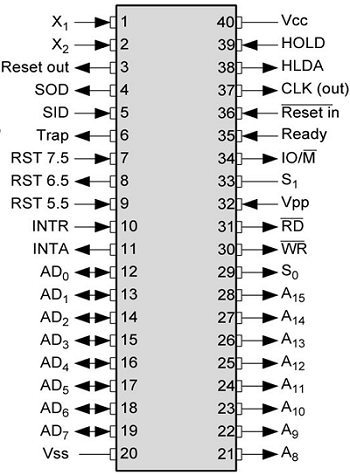

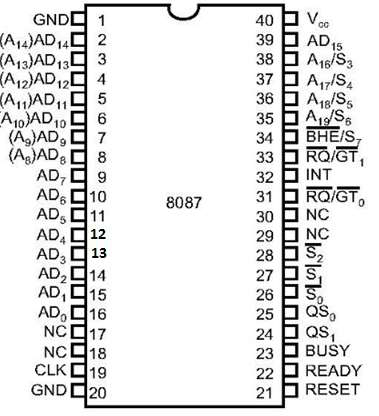

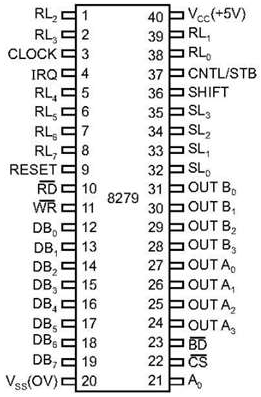

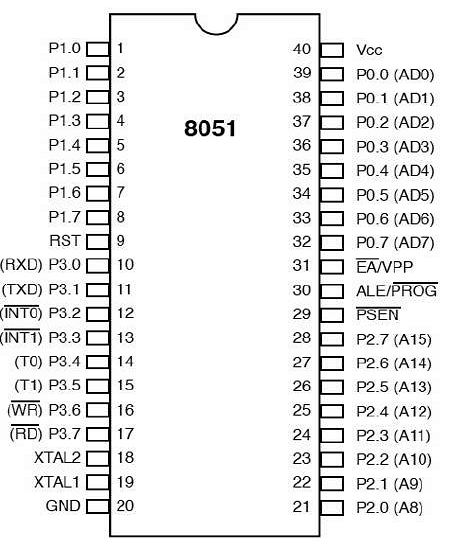

Микропроцессор – 8085 контактов

На следующем рисунке изображена схема контактов микропроцессора 8085 –

Контакты микропроцессора 8085 можно разделить на семь групп:

Адресная шина

A15-A8, он несет самый значительный 8-битный адрес памяти / ввода-вывода.

Шина данных

AD7-AD0, он несет наименее значимый 8-битный адрес и шину данных.

Сигналы управления и состояния

Эти сигналы используются для определения характера операции. Есть 3 сигнала управления и 3 сигнала состояния.

Три управляющих сигнала: RD, WR и ALE.

-

RD – этот сигнал указывает, что выбранное устройство ввода-вывода или запоминающее устройство должно быть прочитано и готово к приему данных, доступных на шине данных.

-

WR – этот сигнал указывает, что данные на шине данных должны быть записаны в выбранную память или место ввода / вывода.

-

ALE – это положительный импульс, генерируемый микропроцессором при запуске новой операции. Когда пульс становится высоким, это указывает на адрес. Когда пульс идет вниз, это указывает на данные.

RD – этот сигнал указывает, что выбранное устройство ввода-вывода или запоминающее устройство должно быть прочитано и готово к приему данных, доступных на шине данных.

WR – этот сигнал указывает, что данные на шине данных должны быть записаны в выбранную память или место ввода / вывода.

ALE – это положительный импульс, генерируемый микропроцессором при запуске новой операции. Когда пульс становится высоким, это указывает на адрес. Когда пульс идет вниз, это указывает на данные.

Три сигнала состояния: IO / M, S0 и S1.

IO / М

Этот сигнал используется для различения операций ввода-вывода и памяти, т. Е. Когда он высокий, это означает работу ввода-вывода, а когда он низкий, то он указывает на работу памяти.

S1 & S0

Эти сигналы используются для определения типа текущей операции.

Источник питания

Есть 2 источника питания – VCC и VSS. VCC указывает источник питания + 5 В, а VSS указывает сигнал заземления.

Тактовые сигналы

Есть 3 тактовых сигнала, то есть X1, X2, CLK OUT.

-

X1, X2 – Кристалл (RC, LC N / W) подключен к этим двум контактам и используется для установки частоты внутреннего тактового генератора. Эта частота внутренне делится на 2.

-

CLK OUT – этот сигнал используется в качестве системных часов для устройств, подключенных к микропроцессору.

X1, X2 – Кристалл (RC, LC N / W) подключен к этим двум контактам и используется для установки частоты внутреннего тактового генератора. Эта частота внутренне делится на 2.

CLK OUT – этот сигнал используется в качестве системных часов для устройств, подключенных к микропроцессору.

Прерывания и внешние сигналы

Прерывания – это сигналы, генерируемые внешними устройствами для запроса микропроцессора на выполнение задачи. Существует 5 сигналов прерывания, т.е. TRAP, RST 7.5, RST 6.5, RST 5.5 и INTR. Мы подробно обсудим прерывания в разделе прерываний.

-

INTA – это сигнал подтверждения прерывания.

-

RESET IN – этот сигнал используется для сброса микропроцессора путем установки счетчика программы на ноль.

-

RESET OUT – этот сигнал используется для сброса всех подключенных устройств при сбросе микропроцессора.

-

ГОТОВ – этот сигнал указывает на то, что устройство готово к отправке или получению данных. Если READY имеет низкий уровень, тогда процессор должен ждать, пока READY поднимется до высокого уровня.

-

HOLD – этот сигнал указывает, что другой мастер запрашивает использование адреса и шин данных.

-

HLDA (HOLD Acknowledge) – указывает на то, что ЦП получил запрос HOLD, и он освободит шину в следующем тактовом цикле. HLDA устанавливается на низкий уровень после снятия сигнала HOLD.

INTA – это сигнал подтверждения прерывания.

RESET IN – этот сигнал используется для сброса микропроцессора путем установки счетчика программы на ноль.

RESET OUT – этот сигнал используется для сброса всех подключенных устройств при сбросе микропроцессора.

ГОТОВ – этот сигнал указывает на то, что устройство готово к отправке или получению данных. Если READY имеет низкий уровень, тогда процессор должен ждать, пока READY поднимется до высокого уровня.

HOLD – этот сигнал указывает, что другой мастер запрашивает использование адреса и шин данных.

HLDA (HOLD Acknowledge) – указывает на то, что ЦП получил запрос HOLD, и он освободит шину в следующем тактовом цикле. HLDA устанавливается на низкий уровень после снятия сигнала HOLD.

Последовательные сигналы ввода / вывода

Есть 2 последовательных сигнала, то есть SID и SOD, и эти сигналы используются для последовательной связи.

-

SOD (строка данных последовательного выхода) – выходной SOD устанавливается / сбрасывается в соответствии с инструкцией SIM.

-

SID (строка последовательного ввода данных) – данные в этой строке загружаются в аккумулятор при каждом выполнении команды RIM.

SOD (строка данных последовательного выхода) – выходной SOD устанавливается / сбрасывается в соответствии с инструкцией SIM.

SID (строка последовательного ввода данных) – данные в этой строке загружаются в аккумулятор при каждом выполнении команды RIM.

8085 адресация режимов и прерываний

Теперь давайте обсудим режимы адресации в микропроцессоре 8085.

Режимы адресации в 8085 году

Это инструкции, используемые для передачи данных из одного регистра в другой регистр, из памяти в регистр и из регистра в память без каких-либо изменений в содержимом. Режимы адресации в 8085 году подразделяются на 5 групп –

Режим немедленной адресации

В этом режиме 8/16-битные данные указываются в самой инструкции как один из ее операндов. Например: MVI K, 20F: означает, что 20F скопирован в регистр K.

Зарегистрировать режим адресации

В этом режиме данные копируются из одного регистра в другой. Например: MOV K, B: означает, что данные в регистре B копируются в регистр K.

Режим прямой адресации

В этом режиме данные напрямую копируются с заданного адреса в регистр. Например: LDB 5000K: означает, что данные по адресу 5000K копируются в регистр B.

Режим косвенной адресации

В этом режиме данные передаются из одного регистра в другой, используя адрес, указанный регистром. Например: MOV K, B: означает, что данные передаются с адреса памяти, указанного регистром, в регистр K.

Подразумеваемый режим адресации

Этот режим не требует никакого операнда; данные определяются самим кодом операции. Например: CMP.

Прерывает в 8085

Прерывания – это сигналы, генерируемые внешними устройствами для запроса микропроцессора для выполнения задачи. Существует 5 сигналов прерывания, т.е. TRAP, RST 7.5, RST 6.5, RST 5.5 и INTR.

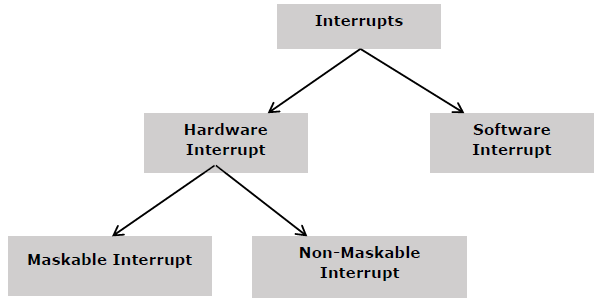

Прерывания классифицируются на следующие группы в зависимости от их параметра –

-

Векторное прерывание – в этом типе прерывания адрес прерывания известен процессору. Например: RST7.5, RST6.5, RST5.5, TRAP.

-

Невекторное прерывание – В этом типе прерывания адрес прерывания не известен процессору, поэтому для прерывания адрес прерывания должен отправляться внешним устройством. Например: INTR.

-

Маскируемое прерывание – в этом типе прерывания мы можем отключить прерывание, написав некоторые инструкции в программу. Например: RST7.5, RST6.5, RST5.5.

-

Немаскируемое прерывание – в этом типе прерывания мы не можем отключить прерывание, записав некоторые инструкции в программу. Например: TRAP.

-

Программное прерывание. В этом типе прерывания программист должен добавить в программу инструкции для выполнения прерывания. В 8085 есть 8 программных прерываний, то есть RST0, RST1, RST2, RST3, RST4, RST5, RST6 и RST7.

-

Аппаратное прерывание. В 8085 в качестве аппаратных прерываний используются 5 контактов прерывания, т. Е. TRAP, RST7.5, RST6.5, RST5.5, INTA.

Векторное прерывание – в этом типе прерывания адрес прерывания известен процессору. Например: RST7.5, RST6.5, RST5.5, TRAP.

Невекторное прерывание – В этом типе прерывания адрес прерывания не известен процессору, поэтому для прерывания адрес прерывания должен отправляться внешним устройством. Например: INTR.

Маскируемое прерывание – в этом типе прерывания мы можем отключить прерывание, написав некоторые инструкции в программу. Например: RST7.5, RST6.5, RST5.5.

Немаскируемое прерывание – в этом типе прерывания мы не можем отключить прерывание, записав некоторые инструкции в программу. Например: TRAP.

Программное прерывание. В этом типе прерывания программист должен добавить в программу инструкции для выполнения прерывания. В 8085 есть 8 программных прерываний, то есть RST0, RST1, RST2, RST3, RST4, RST5, RST6 и RST7.

Аппаратное прерывание. В 8085 в качестве аппаратных прерываний используются 5 контактов прерывания, т. Е. TRAP, RST7.5, RST6.5, RST5.5, INTA.

Примечание. NTA не является прерыванием, оно используется микропроцессором для отправки подтверждения. TRAP имеет самый высокий приоритет, затем RST7.5 и так далее.

Программа обработки прерываний (ISR)

Небольшая программа или подпрограмма, которая при выполнении обслуживает соответствующий источник прерывания, называется ISR.

TRAP

Это немаскируемое прерывание, имеющее самый высокий приоритет среди всех прерываний. По умолчанию он включен, пока не получит подтверждение. В случае сбоя он выполняется как ISR и отправляет данные в резервную память. Это прерывание передает управление в местоположение 0024H.

RST7.5

Это маскируемое прерывание, имеющее второй по приоритетности приоритет среди всех прерываний. Когда выполняется это прерывание, процессор сохраняет содержимое регистра ПК в стек и переходит на адрес 003CH.

RST 6.5

Это маскируемое прерывание, имеющее третий самый высокий приоритет среди всех прерываний. Когда выполняется это прерывание, процессор сохраняет содержимое регистра ПК в стек и переходит по адресу 0034H.

RST 5.5

Это маскируемое прерывание. Когда выполняется это прерывание, процессор сохраняет содержимое регистра ПК в стек и переходит по адресу 002CH.

ВВЕДЕНИ

Это маскируемое прерывание, имеющее самый низкий приоритет среди всех прерываний. Его можно отключить путем сброса микропроцессора.

Когда сигнал INTR становится высоким , могут произойти следующие события:

-

Микропроцессор проверяет состояние сигнала INTR во время выполнения каждой инструкции.

-

Когда сигнал INTR высокий, микропроцессор завершает свою текущую команду и посылает активный сигнал подтверждения прерывания низкого уровня.

-

Когда инструкции получены, микропроцессор сохраняет адрес следующей инструкции в стеке и выполняет полученную инструкцию.

Микропроцессор проверяет состояние сигнала INTR во время выполнения каждой инструкции.

Когда сигнал INTR высокий, микропроцессор завершает свою текущую команду и посылает активный сигнал подтверждения прерывания низкого уровня.

Когда инструкции получены, микропроцессор сохраняет адрес следующей инструкции в стеке и выполняет полученную инструкцию.

Микропроцессор – 8085 инструкций

Давайте посмотрим на программирование микропроцессора 8085.

Наборы инструкций – это коды команд для выполнения некоторых задач. Он классифицируется на пять категорий.

| S.No. | Инструкция и описание |

|---|---|

| 1 | Инструкция по управлению

Ниже приведена таблица со списком команд управления с их значениями. |

| 2 | Логические Инструкции

Ниже приведена таблица со списком логических инструкций с их значениями. |

| 3 | Инструкции по ветвлению

Ниже приведена таблица со списком команд ветвления с их значениями. |

| 4 | Арифметические инструкции

Ниже приведена таблица со списком арифметических инструкций с их значениями. |

| 5 | Инструкция по передаче данных

Ниже приведена таблица со списком команд передачи данных с их значениями. |

Ниже приведена таблица со списком команд управления с их значениями.

Ниже приведена таблица со списком логических инструкций с их значениями.

Ниже приведена таблица со списком команд ветвления с их значениями.

Ниже приведена таблица со списком арифметических инструкций с их значениями.

Ниже приведена таблица со списком команд передачи данных с их значениями.

8085 – Демонстрационные программы

Теперь давайте посмотрим на некоторые демонстрации программ, используя приведенные выше инструкции:

Добавление двух 8-битных чисел

Напишите программу для добавления данных в ячейку памяти 3005H и 3006H и сохраните результат в ячейке памяти 3007H.

Проблема демо –

(3005H) = 14H (3006H) = 89H

Результат –

14H + 89H = 9DH

Код программы можно записать так:

LXI H 3005H: «HL points 3005H» MOV A, M: «Получение первого операнда» INX H: «HL points 3006H» ДОБАВИТЬ М: «Добавить второй операнд» INX H: "HL points 3007H" MOV M, A: «Сохранить результат на 3007H» HLT: «Программа выхода»

Обмен местами памяти

Напишите программу для обмена данными в 5000M и 6000M памяти.

LDA 5000M : "Getting the contents at5000M location into accumulator" MOV B, A : "Save the contents into B register" LDA 6000M : "Getting the contents at 6000M location into accumulator" STA 5000M : "Store the contents of accumulator at address 5000M" MOV A, B : "Get the saved contents back into A register" STA 6000M : "Store the contents of accumulator at address 6000M"

Упорядочить числа в порядке возрастания

Напишите программу, чтобы расположить первые 10 чисел с адреса памяти 3000H в порядке возрастания.

MVI B, 09 :"Initialize counter" START :"LXI H, 3000H: Initialize memory pointer" MVI C, 09H :"Initialize counter 2" BACK: MOV A, M :"Get the number" INX H :"Increment memory pointer" CMP M :"Compare number with next number" JC SKIP :"If less, don’t interchange" JZ SKIP :"If equal, don’t interchange" MOV D, M MOV M, A DCX H MOV M, D INX H :"Interchange two numbers" SKIP:DCR C :"Decrement counter 2" JNZ BACK :"If not zero, repeat" DCR B :"Decrement counter 1" JNZ START HLT :"Terminate program execution"

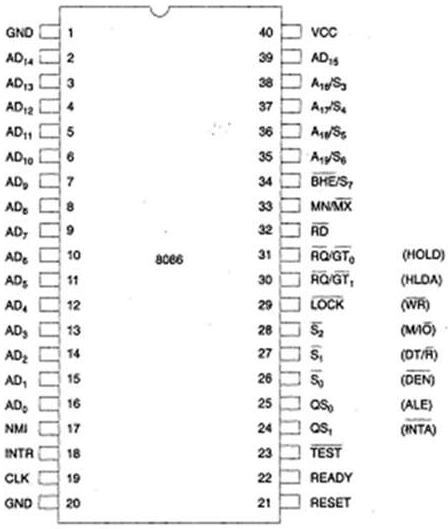

Микропроцессор – 8086 Обзор

Микропроцессор 8086 – это расширенная версия микропроцессора 8085, разработанная Intel в 1976 году. Это 16-разрядный микропроцессор с 20 адресными строками и 16 строками данных, который обеспечивает хранение до 1 МБ. Он состоит из мощного набора команд, который позволяет легко выполнять такие операции, как умножение и деление.

Он поддерживает два режима работы, то есть Максимальный режим и Минимальный режим. Режим Maximum подходит для системы с несколькими процессорами, а режим Minimum подходит для системы с одним процессором.

Особенности 8086

Наиболее характерные особенности микропроцессора 8086:

-

Он имеет очередь команд, которая способна хранить шесть байтов инструкций из памяти, что приводит к более быстрой обработке.

-

Это был первый 16-битный процессор с 16-битным ALU, 16-битными регистрами, внутренней шиной данных и 16-битной внешней шиной данных, что привело к более быстрой обработке.

-

Это доступно в 3 версиях, основанных на частоте операции –

-

8086 → 5 МГц

-

8086-2 → 8 МГц

-

(c) 8086-1 → 10 МГц

-

-

Он использует два этапа конвейерной обработки: этап извлечения и этап выполнения, что повышает производительность.

-

Этап выборки может выполнять предварительную выборку до 6 байтов инструкций и сохранять их в очереди.

-

Этап выполнения выполняет эти инструкции.

-

Имеет 256 векторных прерываний.

-

Он состоит из 29 000 транзисторов.

Он имеет очередь команд, которая способна хранить шесть байтов инструкций из памяти, что приводит к более быстрой обработке.

Это был первый 16-битный процессор с 16-битным ALU, 16-битными регистрами, внутренней шиной данных и 16-битной внешней шиной данных, что привело к более быстрой обработке.

Это доступно в 3 версиях, основанных на частоте операции –

8086 → 5 МГц

8086-2 → 8 МГц

(c) 8086-1 → 10 МГц

Он использует два этапа конвейерной обработки: этап извлечения и этап выполнения, что повышает производительность.

Этап выборки может выполнять предварительную выборку до 6 байтов инструкций и сохранять их в очереди.

Этап выполнения выполняет эти инструкции.

Имеет 256 векторных прерываний.

Он состоит из 29 000 транзисторов.

Сравнение микропроцессора 8085 и 8086

-

Размер – 8085 – это 8-битный микропроцессор, тогда как 8086 – это 16-битный микропроцессор.

-

Адресная шина – 8085 имеет 16-разрядную адресную шину, а 8086 имеет 20-разрядную адресную шину.

-

Память – 8085 может получить доступ до 64 КБ, а 8086 – до 1 МБ памяти.

-

Инструкция – 8085 не имеет очереди команд, тогда как 8086 имеет очередь команд.

-

Конвейерная обработка – 8085 не поддерживает конвейерную архитектуру, в то время как 8086 поддерживает конвейерную архитектуру.

-

I / O – 8085 может адресовать 2 ^ 8 = 256 I / O, тогда как 8086 может обращаться к 2 ^ 16 = 65 536 I / O.

-

Стоимость – стоимость 8085 низкая, а 8086 высокая.

Размер – 8085 – это 8-битный микропроцессор, тогда как 8086 – это 16-битный микропроцессор.

Адресная шина – 8085 имеет 16-разрядную адресную шину, а 8086 имеет 20-разрядную адресную шину.

Память – 8085 может получить доступ до 64 КБ, а 8086 – до 1 МБ памяти.

Инструкция – 8085 не имеет очереди команд, тогда как 8086 имеет очередь команд.

Конвейерная обработка – 8085 не поддерживает конвейерную архитектуру, в то время как 8086 поддерживает конвейерную архитектуру.

I / O – 8085 может адресовать 2 ^ 8 = 256 I / O, тогда как 8086 может обращаться к 2 ^ 16 = 65 536 I / O.

Стоимость – стоимость 8085 низкая, а 8086 высокая.

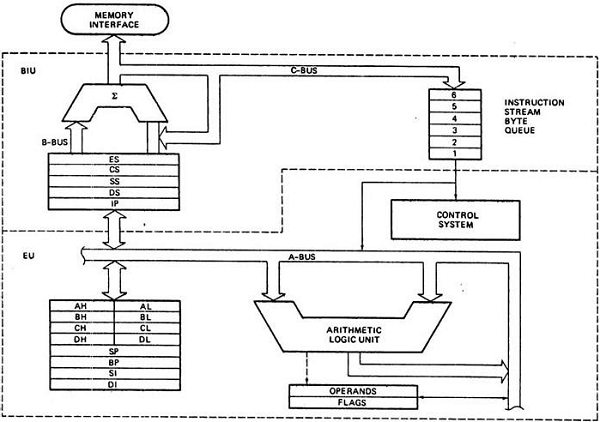

Архитектура 8086 года

Следующая диаграмма изображает архитектуру микропроцессора 8086 –

Микропроцессор – 8086 функциональных блоков

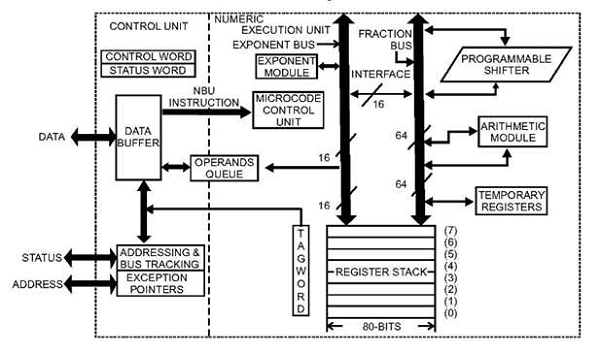

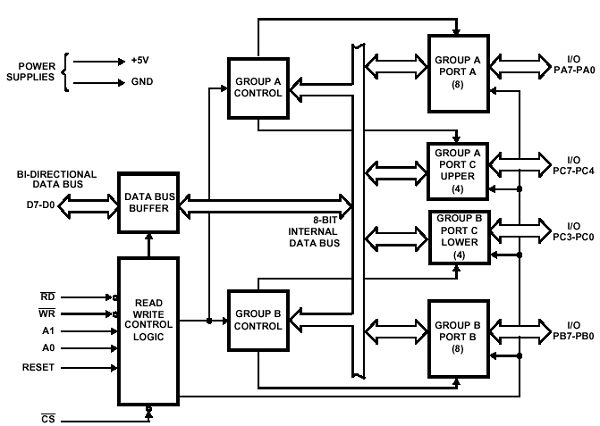

Микропроцессор 8086 разделен на два функциональных блока: EU (исполнительный модуль) и BIU (шинный интерфейсный модуль).

ЕС (исполнительный блок)