По большей части ОЗУ бывает двух размеров: DIMM (Dual In-Line Memory Module), который используется в настольных ПК и серверах, и SO-DIMM (Small Outline DIMM), который используется в ноутбуках и других компьютерах малого форм-фактора. ,

Хотя оба форм-фактора ОЗУ используют одну и ту же технологию и работают одинаково, вы не можете смешивать их. Вы не можете просто вставить DIMM-флешку в слот SO-DIMM, и наоборот (контакты и слоты не совпадают!).

Когда вы покупаете RAM, первое, что нужно понять, это ее форм-фактор. Ничто не имеет значения, если палка не подходит!

Что означает ГДР?

Оперативная память, используемая на вашем компьютере, работает с использованием двойной скорости передачи данных (DDR). Оперативная память DDR означает, что две передачи происходят за такт. Новые типы ОЗУ являются обновленными версиями той же технологии, поэтому модули ОЗУ имеют метки DDR, DDR2, DDR3 и т. Д.

Хотя все поколения RAM имеют одинаковый физический размер и форму, они по-прежнему несовместимы . Вы не можете использовать оперативную память DDR3 в материнской плате, которая поддерживает только DDR2. Аналогично, DDR3 не подходит для слота DDR4. Чтобы избежать путаницы, каждое поколение ОЗУ имеет вырез в контактах в разных местах. Это означает, что вы не можете случайно перепутать ваши модули оперативной памяти или повредить материнскую плату, даже если вы покупаете неправильный тип.

DDR2

DDR2 — это самый старый вид оперативной памяти, с которым вы можете столкнуться сегодня. Он имеет 240 контактов (200 для SO-DIMM). DDR2 был хорошо и действительно заменен, но вы все равно можете купить его в ограниченном количестве, чтобы обновить старые машины. В противном случае DDR2 устареет.

DDR3

DDR3 был выпущен еще в 2007 году. Хотя он был официально заменен DDR4 в 2014 году, вы все равно найдете множество систем, использующих более старый стандарт RAM. Почему? Потому что только в 2016 году (два года после запуска DDR4) системы с поддержкой DDR4 действительно набирали обороты. Кроме того, оперативная память DDR3 охватывает огромный диапазон процессоров, начиная от сокета Intel LGA3636 и заканчивая LGA1151, а также AMD AM3 / AM3 + и FM1 / 2/2 +. (Для Intel это от введения линейки Intel Core i7 в 2008 году до 7- го поколения Kaby Lake!)

Оперативная память DDR3 имеет такое же количество контактов, что и DDR2. Тем не менее, он работает с более низким напряжением и имеет более высокие тайминги (больше на таймингах оперативной памяти в данный момент), поэтому не совместимы. Кроме того, модули DDR3 SO-DIMM имеют 204 контакта по сравнению с 200 контактами DDR2.

DDR4

DDR4 появился на рынке в 2014 году, но еще не полностью контролировал рынок оперативной памяти. Длительный период исключительно высоких цен на оперативную память приостановил модернизацию многих пользователей. Но по мере снижения цен все больше людей переключаются, тем более что последние поколения процессоров AMD и Intel используют исключительно оперативную память DDR4. Это означает, что если вы хотите перейти на более мощный процессор, вам нужна новая материнская плата и новая оперативная память.

DDR4 еще больше понижает напряжение ОЗУ, с 1,5 В до 1,2 В, увеличивая число контактов до 288.

DDR5

DDR5 должен выйти на потребительские рынки в 2019 году. Но учитывая, сколько времени обычно занимает распространение нового поколения RAM, ожидайте услышать об этом больше в 2020 году. Производитель RAM, SK Hynix, ожидает, что DDR5 будет занимать 25% рынка в 2020 г. и 44% в 2021 г.

DDR5 продолжит дизайн с 288-контактным разъемом, хотя напряжение ОЗУ упадет до 1,1 В. Ожидается, что производительность оперативной памяти DDR5 удвоит самый быстрый стандарт предыдущего поколения DDR4. Например, SK Hynix раскрыл технические подробности модуля оперативной памяти DDR5-6400, максимально быстрый из всех возможных по стандарту DDR5.

Но, как и с любым новым компьютерным оборудованием, при запуске ожидайте чрезвычайно высокую цену. Кроме того, если вы подумываете о покупке новой материнской платы , не сосредотачивайтесь на DDR5 . Он пока недоступен, и, несмотря на то, что говорит SK Hynix, Intel и AMD потребуется некоторое время, чтобы подготовиться

RAM Jargon: скорость, задержка, время и многое другое

Вы обернулись вокруг поколения SDRAM, DIMM и DDR. Но как насчет других длинных цепочек чисел в модели RAM? Что они имеют в виду? В чем измеряется ОЗУ? А что насчет ECC и Swap? Вот другие термины спецификации RAM, которые вы должны знать.

Тактовая частота, передача, пропускная способность

Возможно, вы видели ОЗУ, на которую ссылаются два набора чисел, например, DDR3-1600 и PC3-12800. Это и ссылка, и ссылка на генерацию оперативной памяти и ее скорость передачи . Число после DDR / PC и перед дефисом относится к поколению: DDR2 — это PC2, DDR3 — это PC3, DDR4 — это PC4.

Число, соединенное после DDR, относится к числу мегатрансферов в секунду (МТ / с). Например, оперативная память DDR3-1600 работает на скорости 1600 МТ / с. ОЗУ DDR5-6400, о котором говорилось выше, будет работать со скоростью 6400 МТ / с — намного быстрее! Число в паре после ПК относится к теоретической пропускной способности в мегабайтах в секунду. Например, PC3-12800 работает со скоростью 12 800 МБ / с.

Разгон ОЗУ возможен так же, как разгон процессора или видеокарты. Разгон увеличивает пропускную способность оперативной памяти. Производители иногда продают предварительно разогнанную оперативную память, но вы можете разогнать ее самостоятельно. Просто убедитесь, что ваша материнская плата поддерживает более высокую тактовую частоту RAM!

Вы можете быть удивлены, можете ли вы смешивать модули оперативной памяти с разными тактовыми частотами. Ответ в том, что да, вы можете, но все они будут работать на тактовой частоте самого медленного модуля. Если вы хотите использовать более быструю оперативную память, не смешивайте ее со старыми, более медленными модулями. Теоретически вы можете смешивать бренды RAM, но это не рекомендуется. У вас больше шансов встретить синий экран смерти или других случайных сбоев, когда вы смешиваете марки RAM или разные тактовые частоты RAM.

Сроки и задержка

Иногда вы увидите модули оперативной памяти с рядом цифр, например, 9-10-9-27. Эти цифры называются таймингами . Синхронизация ОЗУ — это измерение производительности модуля ОЗУ в наносекундах. Чем ниже цифры, тем быстрее ОЗУ реагирует на запросы.

Первое число (в примере 9) — это задержка CAS. Задержка CAS относится к числу тактовых циклов, необходимых для того, чтобы данные, запрошенные контроллером памяти, стали доступными для вывода данных.

Вы можете заметить, что DDR3 RAM обычно имеет более высокие тактовые номера, чем DDR2, а DDR4 обычно имеет более высокие тактовые номера, чем DDR3. Тем не менее, DDR4 быстрее, чем DDR3, который быстрее, чем DDR2. Странно, правда?

Мы можем объяснить это, используя DDR3 и DDR4 в качестве примеров.

Минимальная частота работы ОЗУ DDR3 составляет 533 МГц, что означает тактовую частоту 1/533000000 или 1,87 нс. При задержке CAS в 7 циклов общая задержка составляет 1,87 x 7 = 13,09 нс. («Нс» означает наносекунды.)

Принимая во внимание, что самая низкая скорость ОЗУ DDR4 составляет 800 МГц, что означает тактовую частоту 1/800000000, или 1,25 нс. Даже если он имеет более высокий CAS из 9 циклов, общая задержка составляет 1,25 x 9 = 11,25 нс. Вот почему это быстрее!

Для большинства людей пропускная способность всегда превосходит тактовую частоту и задержку . Вы получите гораздо больше преимуществ от 16 ГБ ОЗУ DDR4-1600, чем от 8 ГБ ОЗУ DDR4-2400. В большинстве случаев время и задержка являются последними пунктами рассмотрения.

ECC

ОЗУ с исправлением ошибок (ECC) — это особый тип модуля памяти, который предназначен для обнаружения и исправления повреждения данных. ECC ram используется на серверах, где ошибки в критически важных данных могут быть катастрофическими. Например, личная или финансовая информация хранится в оперативной памяти при манипулировании связанной базой данных.

Бытовые материнские платы и процессоры обычно не поддерживают ECC-совместимую оперативную память. Если вы не создаете сервер, который специально требует ОЗУ ECC, вы должны держаться подальше от него.

Сколько оперативной памяти вам нужно?

Давно прошли те времена, когда «640K должно хватить на всех». В мире, где смартфоны регулярно поставляются с 4 ГБ ОЗУ или более, а браузеры, такие как Google Chrome, играют быстро и свободно со своим распределением памяти, экономность ОЗУ — вещь мимо. Средний объем установленной оперативной памяти также увеличивается на всех типах оборудования.

Для большинства людей 4 ГБ — это минимальный объем оперативной памяти, необходимый для компьютера общего пользования. Операционные системы тоже имеют разные спецификации. Например, вы можете запустить Windows 10 только на 1 ГБ ОЗУ, но ваш пользовательский опыт будет вялым. И наоборот, многочисленные дистрибутивы Linux работают очень хорошо с меньшими объемами оперативной памяти

Если вы обнаружите, что одновременно открыты шесть документов Word, не можете заставить себя закрыть эти 60 вкладок в Google Chrome, возможно, вам понадобится как минимум 8 ГБ ОЗУ. То же самое происходит, если вы хотите использовать виртуальную машину.

16 ГБ ОЗУ должно превышать потребности большинства. Но если вы продолжите работу утилит в фоновом режиме, с множеством вкладок браузера и всего остального, вы по достоинству оцените дополнительную емкость ОЗУ. Очень немногие люди нуждаются в 32 ГБ ОЗУ, но, как говорится, чем больше, тем больше.

Обновление ОЗУ, безусловно, является одним из самых простых способов мгновенного повышения производительности. максимально повысить производительность

Понимание всего о оперативной памяти

Теперь вы знаете разницу между оперативной памятью DDR2, DDR3 и DDR4. Вы можете сказать DIMM от SO-DIMM, и вы знаете, как определить RAM с более высокими скоростями передачи и более высокой пропускной способностью. На этом этапе вы, по сути, являетесь экспертом в области ОЗУ, поэтому в следующий раз вы не будете испытывать перегрузку, пытаясь купить больше ОЗУ или совершенно новую систему.

Действительно, если у вас правильный форм-фактор и соответствующее поколение ОЗУ, вы не ошибетесь. Время и латентность играют свою роль, но способность — король. И если есть сомнения, больше ОЗУ лучше, чем быстрее ОЗУ важнее

Как разогнать оперативную память: исчерпывающее руководство

Это обеспечит прирост производительности безо всяких вложений.

Какие характеристики определяют скорость работы оперативной памяти

Скорость работы компьютера зависит от объёма оперативной памяти. А насколько быстро она сама даёт записывать и считывать данные, покажут эти характеристики.

Эффективная частота передачи данных

Скорость работы памяти зависит от количества операций передачи данных, которые можно провести за одну секунду. Чем выше эта характеристика, тем быстрее работает память.

Формально скорость измеряется в гигатрансферах (GT/s) или мегатрансферах (MT/s). Один трансфер — одна операция передачи данных, мегатрансфер — миллион таких операций, гигатрансфер — миллиард.

Но почти всегда скорость указывают в мегагерцах или гигагерцах — производители решили, что покупателям так будет понятнее. Если на вашу планку памяти нанесена, например, маркировка DDR4‑2133, то её скорость передачи данных — 2 133 MT/s или 2 133 МГц.

Но эффективная частота передачи данных памяти DDR вдвое выше её тактовой частоты. Собственно, DDR — это double data rate, удвоенная скорость передачи данных.

В таких модулях данные за каждый такт передаются дважды: импульс считывается и по фронту сигнала, и по его спаду, то есть один цикл — это две операции. Таким образом, реальная частота, на которой работает память DDR-2666 — 1 333 MT/s или 1 333 МГц.

Если у вас установлены планки памяти с разной частотой, то система будет работать на наименьшей из них. Конечно же, материнская плата должна поддерживать эту частоту.

Тайминги

CAS‑тайминги (Column Access Strobe) — это задержки в процессе работы оперативной памяти. Они показывают, сколько тактов нужно модулю памяти для доступа к битам данных. Чем ниже тайминги, тем лучше.

По сути, память — это прямоугольная таблица, которая состоит из ячеек в строках и столбцах. Чтобы получить доступ к данным, нужно найти правильную строку, открыть её и обратиться к ячейке в определённом столбце.

Обычно тайминги записываются в таком формате: 15‑17‑17‑39. Это четыре разных параметра:

- Собственно, CAS Latency — задержка сигнала между отправкой адреса столбца в память и началом передачи данных. Отражает время, за которое будет прочитан первый бит из открытой строки.

- RAS to CAS Delay — минимальное количество тактов между открытием строки памяти и доступом к её столбцам. По сути, это время на открытие строки и чтение первого бита из неё.

- RAS Precharge Time — минимальное количество тактов между подачей команды предварительной зарядки (закрытием строки) и открытием следующей строки. Отражает время до считывания первого бита памяти из ячеек с неверной открытой строкой. В этом случае неверную строку нужно закрыть, а нужную — открыть.

- DRAM Cycle Time tRAS/tRC — отношение интервала времени, в течение которого строка открыта для переноса данных, ко времени, в течение которого завершается полный цикл открытия и обновления строки. Этот параметр отражает быстродействие всей микросхемы памяти.

Если у оперативной памяти высокая тактовая частота и большие тайминги, она может работать медленнее, чем вариант с меньшей частотой, но и более низкими таймингами. Вы можете разделить тактовую частоту на CAS Latency (первое число в строке таймингов) и понять, сколько инструкций в секунду способна выполнить память. Это позволит оценить, насколько она быстрая.

Напряжение

В документации к оперативной памяти вы можете увидеть много различных параметров: напряжение контроллера (SOC), тренировки памяти при запуске системы (DRAM Boot), источника опорного напряжения (Vref) и так далее. Для разгона важен в первую очередь SOC. Он зависит от класса памяти — нормой считаются такие значения:

- DDR2 — 1,8 В;

- DDR3 — 1,5 В;

- DDR4 — 1,2 В.

Также для каждого класса памяти есть пиковые значения напряжений, которые при разгоне превышать не стоит:

- DDR2 — 2,3 В;

- DDR3 — 1,8 В;

- DDR4 — 1,5 В.

При повышении частоты оперативной памяти потребуется увеличенное напряжение. Но чем оно выше, тем больше риск преждевременного выхода модулей из строя.

Ранг

Оперативная память бывает одно-, двух- и четырехранговой. Ранг — это число массивов из микросхем памяти, распаянных на одном модуле. Ширина одного массива (банка), как правило, равна 64 битам, в системах с ЕСС (кодом коррекции ошибок) — 72 бита.

Одноранговые модули (single rank) обычно включают 4 или 8 чипов на одной планке. Двухранговые (double rank) — 16 таких чипов. Четырехранговые (quad rank) — 32 чипа, и такой формат встречается достаточно редко.

Обычно этот показатель помечается буквой в названии: S (single) — одноранговая, D (double) — двухранговая, Q (quad) — четырехранговая.

Одноранговые чипы обычно дешевле и имеют больше перспектив для разгона. Двухранговые модули изначально работают с большей производительностью, но прирост при разгоне будет меньше.

Любую ли оперативную память можно разогнать

Это зависит в первую очередь от материнской платы. Если она поддерживает оверклокинг (разгон), то, скорее всего, и с разгоном памяти проблем не будет.

Материнские платы на базе чипсетов B350, B450, B550, X370, X470, X570 для процессоров AMD поддерживают разгон, на А320 — нет. На этой странице вы сможете уточнить, есть ли возможность оверклокинга у вашей модели.

Для систем с процессорами Intel для оверклокинга подходят платы на чипсетах Х- и Z‑серий. Модели из линеек W-, Q-, B- и H‑серий разгон не поддерживают. Уточнить данные по вашей материнской плате можно здесь.

Считается, что оперативная память Samsung обеспечивает наиболее высокий прирост при разгоне. Прирост производительности чипов Hynix и Micron будет меньше.

Подчеркнём: речь идёт именно о чипах. Некоторые бренды, например Kingston или Crucial, могут выпускать память на чипах Samsung, Hynix или Micron.

Вопрос лишь в том, зачем вам разгонять память. Если вы таким образом хотите ускорить сёрфинг в интернете, то вряд ли достигнете заметных результатов. А вот для повышения FPS в играх, ускорения обработки фото в Adobe Lightroom и видео в Adobe AfterEffects или Premiere разгон оправдан — можно «выжать» рост производительности на 15–20%.

Отметим также, что у процессоров AMD Ryzen частота оперативной памяти связана с частотой внутренней шины, которой соединяются два блока ядер. Поэтому для систем на базе AMD разгон напрямую влияет на производительность центрального процессора.

Но в любом случае гарантия производителей не распространяется на память, параметры которой вы изменили. Так что любой разгон вы делаете на свой страх и риск.

Как подготовиться к разгону оперативной памяти

Чтобы добиться результата и не навредить компьютеру, выполните эти шаги.

Почистите компьютер

Любой разгон ведёт к повышению температуры комплектующих. Чтобы система охлаждения эффективно справилась с этим, проведите генеральную уборку внутри системного блока или ноутбука. На этой странице вы найдёте инструкцию для ноутбука, с ПК всё окажется даже проще: комплектующие на виду, разбирать системный блок легче.

Установите ПО

Эти утилиты расскажут о характеристиках вашей системы и помогут протестировать её после разгона. Вам точно потребуется программа для определения параметров памяти и бенчмарк для тестов. Рекомендуем такие варианты ПО:

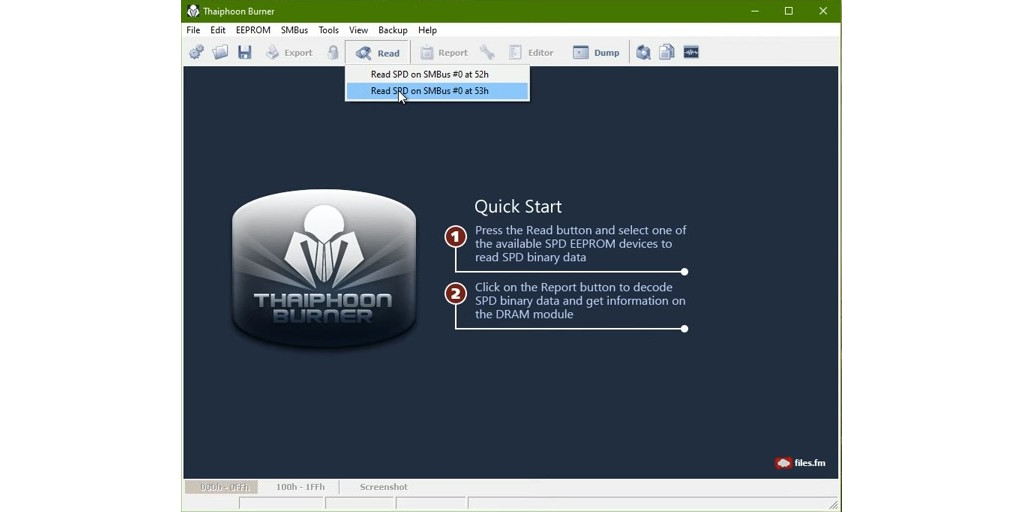

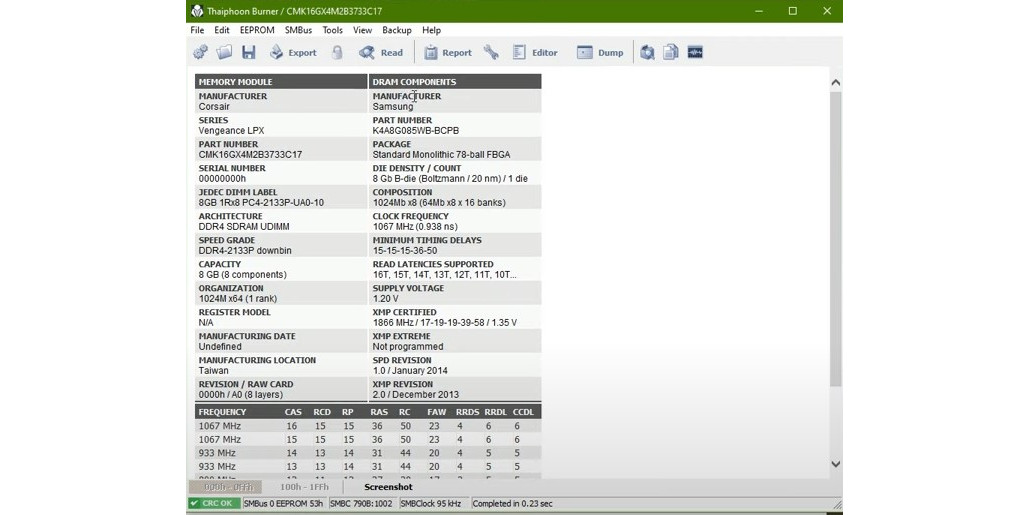

- Thaiphoon Burner — пожалуй, самая популярная в среде оверклокеров утилита для определения параметров памяти. Цена — от 26 долларов в год.

- CPU‑Z — небольшая бесплатная программа, которая поможет уточнить характеристики памяти и системы в целом.

- Аida64 — также показывает параметры системы и включает бенчмарки для тестирования. На официальном сайте есть платные варианты и бесплатные демоверсии.

- DRAM Calculator for Ryzen — бесплатная утилита, поможет выставить оптимальные параметры разгона оперативной памяти для систем на базе AMD Ryzen. Также ПО включает бенчмарк для тестирования памяти, который подходит и для систем на базе процессоров Intel.

- Prime95 — бесплатный бенчмарк для тестирования стабильности системы: он хорошо нагружает и процессор, и оперативную память. При использовании нужно выбрать вариант Blend, чтобы добиться значительной нагрузки на память.

- MemTest86 — бенчмарк, в котором вы найдёте больше данных и алгоритмов для проверки. Для работы программы потребуется флешка — на неё вы запишете образ диска с тестами. Затем нужно загрузить компьютер с флеш‑накопителя (выставить в BIOS / UEFI загрузку с USB) и запустить тесты. Бесплатной версии достаточно для разгона ОЗУ.

Найдите свежую версию BIOS / UEFI материнской платы

Обновите программное обеспечение материнской платы перед разгоном. Загрузить свежий BIOS / UEFI можно с сайта производителя.

Как правило, новые версии работают стабильнее, в них меньше ошибок и факторов риска. К тому же старые прошивки некоторых моделей плат могут не поддерживать разгон памяти, а новые — уже включают эту функцию.

Как разогнать оперативную память в BIOS

Разгон в BIOS — самый универсальный способ. Он требует много усилий и времени, так как подбирать параметры приходится вручную. Порой на достижение оптимальных характеристик может уйти день‑другой. Но работает всегда — разумеется, если ваша материнская плата поддерживает оверклокинг. Главное — не увеличивать напряжение выше пиковых значений и не игнорировать ошибки в тестах стабильности системы.

Определите характеристики оперативной памяти

В Thaiphoon Burner нажмите Read и выберите нужный модуль памяти. Характеристики показываются отдельно для каждого из них.

1 / 0

2 / 0

В CPU‑Z эти данные представлены на вкладке SPD. В верхней части — тип памяти, её частота, ранг, сведения о производителе и дате выпуска. В нижней — тайминги.

Эта же информация есть в Aida64: в пункте «Системная плата» — SPD:

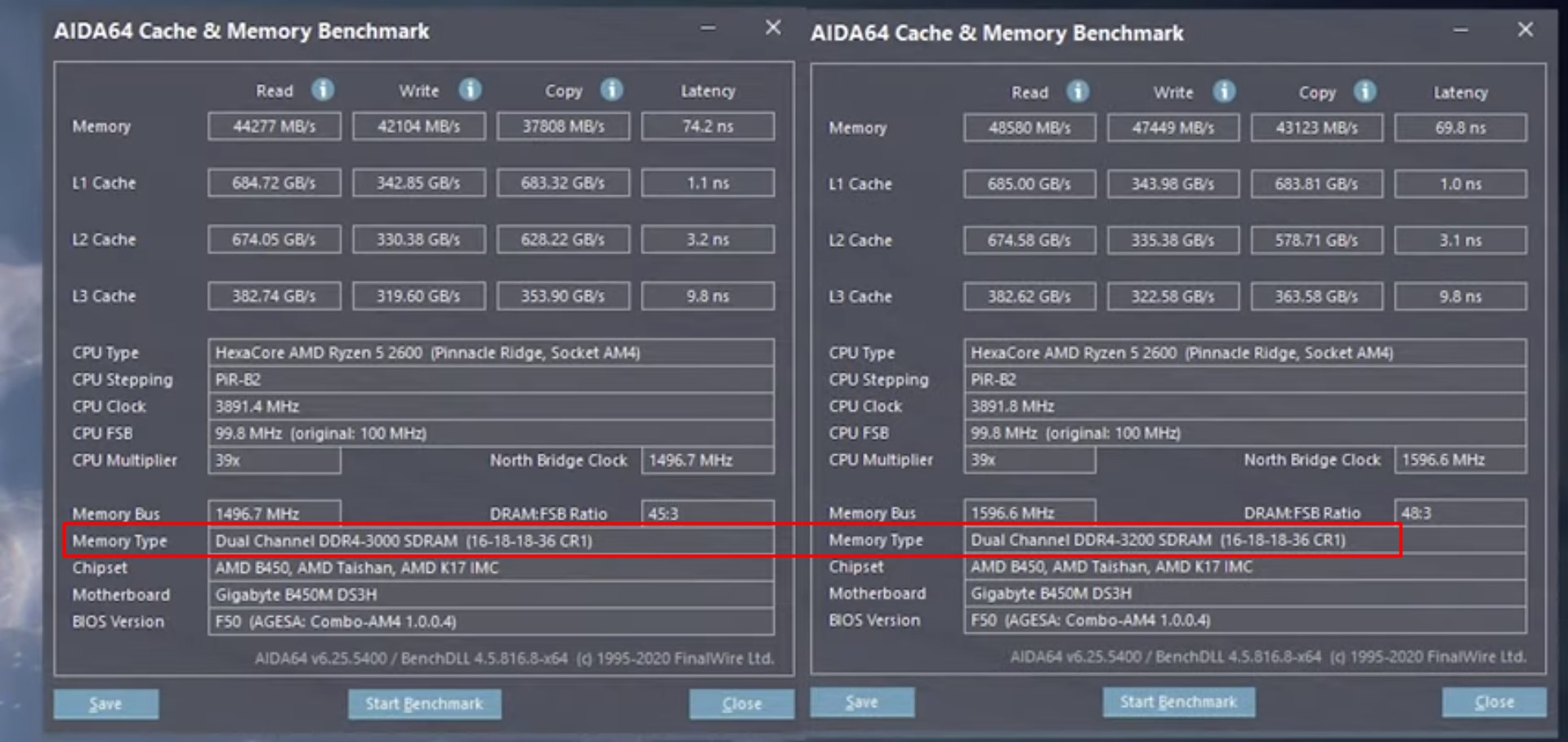

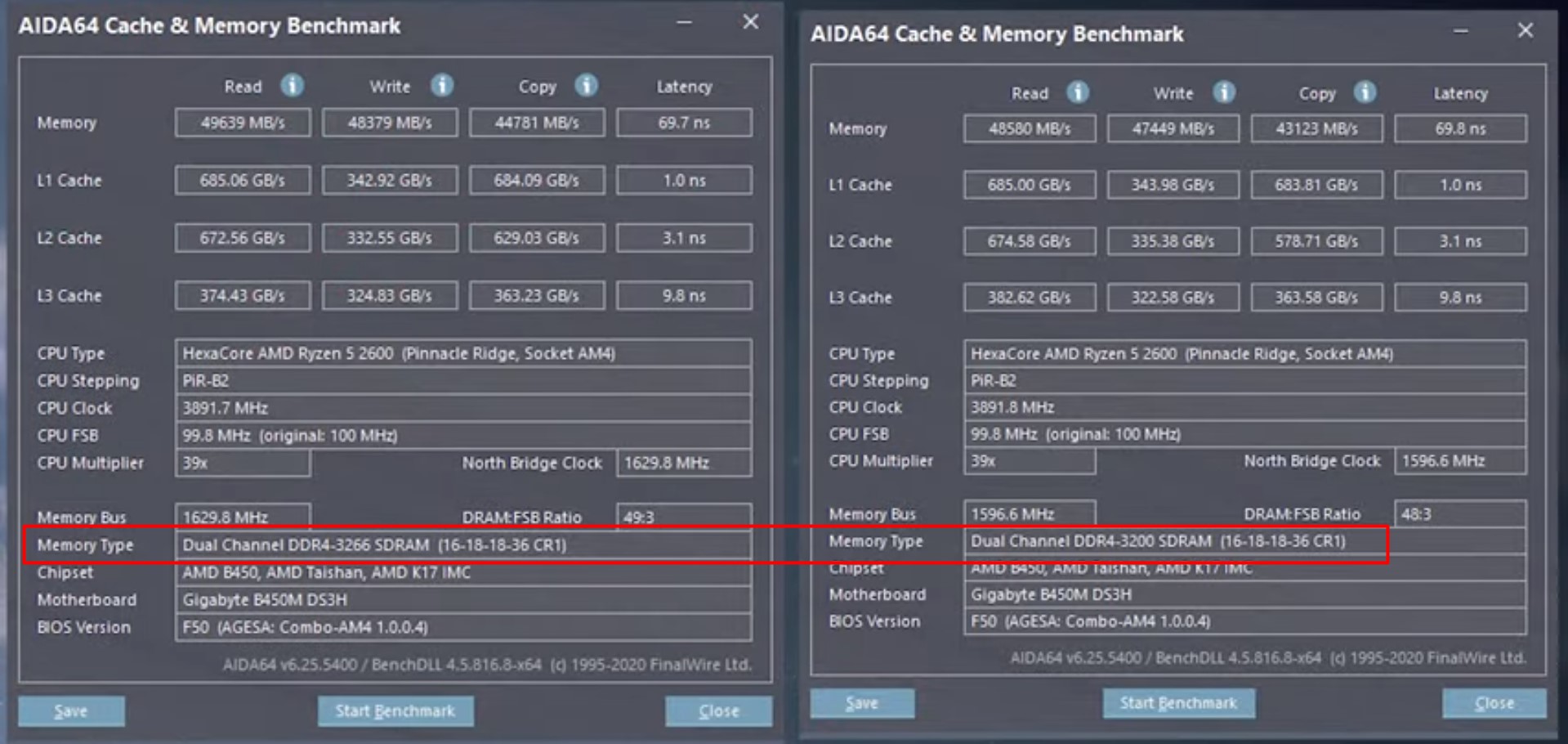

Оцените производительность памяти в бенчмарке

Запустите бенчмарк для оценки скорости работы модулей до разгона. Например, в разделе «Тесты» Aida64 доступны варианты «Чтение из памяти», «Запись в память», «Копирование в памяти» и «Задержка памяти». Дождитесь окончания каждого теста и сохраните результаты — запишите или сделайте скриншоты.

Увеличьте напряжение и частоту

Поднимите рабочее напряжение модулей памяти. Для самого распространённого сегодня стандарта DDR4 нормой считается 1,2 В, пиковым — 1,5 В, значит, разгон можно проводить в пределах 1,35–1,45 В.

Рекомендуем также увеличить напряжение контроллера (VCORE SOC для AMD, VCCSA для Intel), если материнская плата не делает это автоматически. Параметр должен быть в пределах 1,05–1,1 В.

Вы можете увеличить и VCCIO на 0,05–0,1 В. Дополнительное напряжение может сделать систему стабильнее.

Затем постепенно повышайте частоту памяти. Для Ryzen многое зависит от архитектуры процессора. Так, в системах с чипами на микроархитектуре Zen оперативную память можно разогнать до 3 466 МГц, на Zen+ — до 3 533 МГц, на Zen2 — до 3 800 МГц. Для Zen3, которая появилась в продаже в ноябре, ожидается разгон памяти до 4 000 МГц и выше.

Примерные значения вы можете определить в DRAM Calculator for Ryzen для систем на базе процессора AMD. Вам нужно указать микроархитектуру (Zen, Zen+, Zen2, Zen3), тип чипа памяти, ранг (1 или 2), количество модулей и чипсет материнской платы.

Напомним: характеристики памяти детально описаны в Thaiphoon Burner. Семейство процессора и материнской платы найдёте в CPU‑Z или Aida64.

После того как вы установили основные параметры системы в DRAM Calculator for Ryzen, нажмите R‑XMP, чтобы он выполнил базовые расчёты. А затем определите нужные настройки для безопасного (Calculate Safe), быстрого (Calculate Fast) или экстремального разгона (Calculate Extreme).

Для Intel аналогов DRAM Calculator for Ryzen пока нет. Но если вы пользуетесь какими‑то средствами, которые облегчают подбор параметров, напишите о них в комментариях.

Разработчики DRAM Calculator for Ryzen предлагают пользователям делиться результатами разгона и собирают статистику в таблицы:

- Zen;

- Zen+;

- Zen2.

Не рекомендуем сразу увеличивать частоту оперативной памяти выше значений, которые поддерживает процессор. Характеристики процессоров Intel ищите на этой странице.

На сайте AMD вы также можете найти информацию о конкретной модели чипсета.

Перезагрузите компьютер и проверьте результат

Прежде всего запустите бенчмарк и посмотрите, увеличились ли результаты. Если нет, верните предыдущие значения — вероятно, вы достигли максимальной частоты работы памяти. Если показатели выросли, запустите тест стабильности системы, например из DRAM Calculator for Ryzen.

Если в тесте ошибок не будет, можете начать более фундаментальные испытания. Пары часов в Prime95 или другом требовательном к памяти бенчмарке будет достаточно. Только если в течение длинного стресс‑теста вы не поймали BSOD («синий экран смерти») или другие ошибки, можете перейти к следующему этапу разгона. В ином случае возвращайте предыдущие значения.

Повторите

Повышайте частоту оперативной памяти, пока компьютер работает стабильно. Если же он не запустился после перезагрузки, верните предыдущие значения параметров, которые вы меняли.

Уменьшите тайминги

Когда вы достигли максимально возможных значений частоты работы оперативной памяти, снижайте базовые тайминги (первые четыре значения) на единицу и снова тестируйте систему. Остановиться стоит, когда вы перестанете видеть прирост производительности или когда компьютер не сможет стабильно работать.

1 / 0

2 / 0

Как разогнать оперативную память с помощью XMP‑профиля

XMP‑профиль (eXtreme Memory Profile — экстремальный профиль памяти) — это параметры для разгона оперативной памяти, заданные производителем. Фактически это «одобренный оверклокинг»: мощность будет выше, чем с изначальными заводскими настройками, а риски вывести систему из строя минимальны.

Это, пожалуй, самый простой способ разгона. Если, конечно, XMP‑профили доступны для вашего ПК.

Проверьте, поддерживает ли система XMP‑профили

Зайдите в BIOS / UEFI и перейдите на страницу настроек памяти. Если здесь есть пункт вроде Memory Profile и в нём доступны варианты XMP‑профилей, значит, ваша система поддерживает эту возможность. В самом профиле вы можете увидеть конкретные значения параметров работы оперативной памяти.

Оцените производительность памяти в бенчмарке

Откройте DRAM Calculator for Ryzen, запустите Membench и выберите подходящий тест. Рекомендуем Easy, если у вас до 8 ГБ оперативной памяти, и Memtest — если больше.

Вы также можете запустить тесты в Aida64 или других бенчмарках.

Примените XMP‑профиль

Переключите конфигурацию в BIOS / UEFI со стандартной на нужный XMP‑профиль. Примените настройки и перезагрузите систему.

На некоторых платах профили включаются иначе. Например, в BIOS / UEFI материнских плат ASUS их можно активировать в разделе AI Tweaker. В BIOS / UEFI игровых материнских плат MSI этот пункт вынесен на главную страницу или на вкладку Extreme Tweaker.

Оцените результат

Снова запустите бенчмарк и оцените рост показателей. Затем запустите тест стабильности системы (Prime95 и другие) — не менее чем на два часа, а лучше — на 12–24 часа.

Если всё прошло успешно, используйте этот профиль или попробуйте следующий. Затем сравните результаты и выберите тот, который обеспечит вам большую производительность.

Если система не запустилась, поэкспериментируйте с другим профилем или верните заводские настройки. Обычно первый вариант немного повышает производительность системы, а второй и последующие обеспечивают более экстремальный разгон.

Как разогнать оперативную память с помощью AMD Ryzen Master

AMD Ryzen Master — это утилита для комплексного разгона систем на базе процессоров AMD Ryzen. Оверклокинг здесь похож на разгон памяти в BIOS. Но интерфейс универсальнее и есть готовый бенчмарк для тестов.

В секции Memory Control вы можете установить нужные параметры производительности. При выборе настроек рекомендуем отталкиваться от значений, которые выдаст DRAM Calculator for Ryzen.

По завершении настройки сохраните профиль, а затем нажмите Apply & Test. Встроенный бенчмарк поможет проверить стабильность и продуктивность работы системы.

Скачать AMD Ryzen Master →

Читайте также 👨💻💿⚙️

- Как переустановить Windows: пошаговая инструкция

- Как разогнать процессор и не навредить компьютеру

- Как разогнать видеокарту безопасно

- 10 лучших программ для создания загрузочной флешки

- Что делать, если тормозит компьютер с Windows

Оперативная память

(оперативное запоминающее устройство,

ОЗУ) — часть памяти ЭВМ, в которую

процессор может обратиться за одну

операцию (jump, move и т. п.). Она

предназначена для временного хранения

данных и команд, необходимых процессору

для выполнения им операций. Оперативная

память передаёт процессору данные

непосредственно, либо через кеш-память.

Каждая ячейка оперативной памяти имеет

свой индивидуальный адрес.

Система управления

оперативной памятью должна поддерживать

[3]:

-

перемещение

программ из одной области памяти в

другую (поддержка относительности

адреса); -

защиту одного

процесса от влияния других; -

совместное

использование процессами памяти для

взаимодействия (обратная защита) –

механизмы межпроцессного взаимодействия

(IPC); -

поддержка логических

операций с адресацией; -

поддержка физических

операций с адресацией.

Пусть процесс

занимает непрерывную область основной

памяти. ОС необходимо знать местоположение

управляющей информации процесса и стека

исполнения, а также точки входа для

начала выполнения процесса. Поскольку

управлением памятью занимается ОС и

она же размещает процесс в основной

памяти, соответствующие адреса она

получает автоматически. Однако помимо

получения ОС указанной информации,

процесс должен иметь возможность

обращаться к памяти в самой программе.

Так команды ветвления содержат адреса,

указывающие на команды, которые должны

быть выполнены после них; команды

обращения к данным – адреса байтов и

слов, с которыми они работают. ОС переводит

ссылки в коде программы (логические

адлеса) в реальные физические адреса,

соответствующие текущему расположению

процесса в основной памяти рис. 13.

00000000 h

FFFFFFFF h

Рис. 13.Образ процесса

в оперативной памяти

Система управления

памятью характеризуется :

1. Стратегией

выборки. Страница загружается в

оперативную память, как по требованию

процесса, так и с использованием стратегии

предварительной выборки, при которой

происходит загрузка страниц кластерами

[3].

2.

Стратегией размещения. При использовани

сегментации все вновь загруженные

сегменты должны быть размещены в

доступном адресном пространстве.

3. Стратегией

замещения. При заполнении памяти следует

принимать решение о том, какая страница

будет замещена загружаемой в оперативную

память новой страницей.

4. Стратегией

очистки. Изменённые страницы процесса

должны быть записаны (сохранены) при их

замещении.

5.

Управление загрузкой: заключается в

определении количества процессов,

которые должны быть резидентны в

оперативной памяти в данный момент.

6. Управление

резидентным множеством процессов. ОС

определяет сколько памяти отводить

процессу при загрузке его в оперативную

память. Память может быть выделена

статически в момент создания процесса,

либо изменяться динамически в процессе

работы [3].

Рассмотрим случай,

когда основная память разделена на

одинаковые блоки относительно небольшого

фиксированного размера. Тогда блоки

процесса, известные как страницы (pages),

могут быть связны со свободными блоками

памяти, известными как кадры (frames)

или фрэймы. Каждый кадр оперативной

памяти может содержать одну страницу

процесса. В каждый момент времени

некоторые из кадров памяти используются,

а некотрые свободны. ОС содержит

список свободных кадров (рис.14 а).

|

Кадр |

Осн.Пам. |

Кадр |

Осн.Пам. |

Кадр |

Осн.Пам. |

Кадр |

Осн.Пам. |

Кадр |

Осн.Пам. |

Кадр |

Осн.Пам. |

|

0 |

0 |

A.0 |

0 |

A.0 |

0 |

A.0 |

0 |

A.0 |

0 |

A.0 |

|

|

1 |

1 |

A.1 |

1 |

A.1 |

1 |

A.1 |

1 |

A.1 |

1 |

A.1 |

|

|

2 |

2 |

A.2 |

2 |

A.2 |

2 |

A.2 |

2 |

A.2 |

2 |

A.2 |

|

|

3 |

3 |

A.3 |

3 |

A.3 |

3 |

A.3 |

3 |

A.3 |

3 |

A.3 |

|

|

4 |

4 |

4 |

B.0 |

4 |

B.0 |

4 |

4 |

D.0 |

|||

|

5 |

5 |

5 |

B.1 |

5 |

B.1 |

5 |

5 |

D.1 |

|||

|

6 |

6 |

6 |

B.2 |

6 |

B.2 |

6 |

6 |

D.2 |

|||

|

7 |

7 |

7 |

7 |

C.0 |

7 |

C.0 |

7 |

C.0 |

|||

|

8 |

8 |

8 |

8 |

C.1 |

8 |

C.1 |

8 |

C.1 |

|||

|

9 |

9 |

9 |

9 |

C.2 |

9 |

C.2 |

9 |

C.2 |

|||

|

10 |

10 |

10 |

10 |

C.3 |

10 |

C.3 |

10 |

C.3 |

|||

|

11 |

11 |

11 |

11 |

11 |

11 |

D.3 |

|||||

|

12 |

12 |

12 |

12 |

12 |

12 |

D.4 |

|||||

|

13 |

13 |

13 |

13 |

13 |

13 |

||||||

|

14 |

14 |

14 |

14 |

14 |

14 |

||||||

|

а) |

б) |

в) |

г) |

Д) |

е) |

Рис. 14 Распределение

страниц процессов по свободным кадрам:

а) 15 доступных

кадров, б) загрузка процесса А, в) загрузка

процесса В, г) загрузка порцесса С, д)

выгрузка процесса В, е) загрузка процесса

D.

Процесс А, хранящийся

на диске, сотоит из четырех страниц.

Когда приходит время загрузить его в

память, ОС находит четыре свободных

кадра и загружает страницы процесса А

в эти кадры (рис. 14 б). Затем загружается

процесс В, состоящий из трех страниц, и

процесс С, сотоящий из четырех страниц.

После этого процесс В приостанавливается

и выгружается из основной памяти. Затем

наступает момент, когда все процессы в

памяти оказываются заблокированными,

и ОС загружает в память новый процесс

D,

состящий из пяти сраниц. Но непрерывной

области кадров в памяти нет и ОС используя

таблицу сраниц процесса (она есть у

каждого процесса) размещает страницы

процесса D

в кадрах 4,5,6,11,12 (рис. 14 е).

|

Таблица страниц процесса А |

Таблица страниц процесса B |

Таблица страниц процесса C |

Таблица страниц процесса D |

Список свободных кадров |

|||||

|

0 |

0 |

0 |

‑ |

0 |

7 |

0 |

4 |

13 |

|

|

1 |

1 |

1 |

‑ |

1 |

8 |

1 |

5 |

14 |

|

|

2 |

2 |

2 |

‑ |

2 |

9 |

2 |

6 |

||

|

3 |

3 |

3 |

10 |

3 |

11 |

||||

|

4 |

12 |

Рис. 15. Структуры

данных процессов рис. 14е

Размеры оперативной

памяти персональных компьютеров

сегодняшнего дня постоянно отстают от

запросов прикладного программного

обеспечения. В имеющийся объем оперативной

памяти не всегда удается загрузить

операционную систему и несколько

прикладных программ, особенно если их

много и они громоздкие.

Выход из этой

ситуации в использовании концепции

виртуальной памяти. Виртуальная память

— это логический ресурс, эмулирующий

оперативную память путем использования

как физической оперативной, так и

дисковой памяти. Благодаря этому емкость

виртуальной памяти получается больше

реальной. Активный программный код

должен находиться в физической оперативной

памяти, остальной же код может временно

храниться в ее «продолжении» на жестком

диске. Когда управление передается

фрагменту кода, хранящемуся на жестком

диске, он загружается в физическую

память. Если места в ней недостаточно,

это приведет к выгрузке на диск пассивного

кода. Процесс загрузки и выгрузки

программного кода называется свопингом,

или подкачкой. Его размер файла подкачки

может динамически изменяется в зависимости

от нужд системы, он не обязательно должен

быть непрерывным и может находиться на

сжатом диске. Виртуальная память имеет

страничную организацию, поддерживаемую

процессором. Страницей является блок

памяти фиксированной длины. Процесс

может занимать одну или несколько

страниц памяти.

Страничная

организация памяти. Каждый

процесс имеет свою собственную таблицу

страниц, которая создается при загрузке

всех страниц процесса в основную память.

Каждая запись в таблице страниц содержит

номер кадра соответствующей страницы

в памяти (рис.15). Поскольку в основной

памяти могут находиться только некоторые

из страниц процесса, в каждой записи

таблицы должен иметься бит Р, указывающий

на присутствие соответствующей страницы

в основной памяти. Если данная страница

располагается в основной памяти, то в

записи таблицы содержится номер ее

кадра.

Рис. 15. Типичные

форматы систем управления памятью

Другим управляющим

битом в записи таблицы страниц является

бит модификации — М, который указывает,

было ли изменено содержимое данной

страницы со времени последней загрузки

в основную память. Если изменений не

было, то когда наступит время замены

страницы в занимаемом ею в данный момент

кадре, записывать эту страницу на диск

не следует, так как на диске уже имеется

ее точная копия. В записи таблицы страниц

могут быть и другие управляющие биты,

например, служащие для целей защиты или

совместного использования памяти на

уровне страниц.

Базовый механизм

чтения слова из памяти включает в себя

трансляцию логического, адреса, состоящего

из номера страницы и смещения, в физический

адрес, который представляет собой номер

кадра и смещение, с использованием

таблицы страниц (рис.16). Таблица страниц

должна располагаться в основной памяти.

При выполнении процесса стартовый адрес

его таблицы страниц хранится в регистре,

а номер страницы из виртуального адреса

используется в качестве индекса элемента,

в котором ищется соответствующий номер

кадра.

Рис. 16. Страничная

организация памяти

Затем этот номер

объединяется со смещением из виртуального

адреса для получения реального физического

адреса интересующей нас ячейки памяти.

Большинство схем виртуальной памяти

хранят таблицы страниц не в реальной,

а в виртуальной памяти. Это означает,

что сами таблицы страниц становятся

объектами страничной организации, как

и любые другие страницы. При работе

процесса как минимум часть его таблицы

страниц должна располагаться в основной

памяти, в том числе запись о странице,

выполняющейся в настоящий момент [3].

Некоторые процессоры

используют двухуровневую схему для

больших таблиц страниц. При такой схеме

имеется каталог таблиц страниц, в котором

каждая запись указывает на таблицу

страниц. Каждый виртуальный адрес

вызывает обращение к двум физическим

адресам: для выборки соответствующей

записи из таблицы страниц и для обращения

к адресуемым данным. Для преодоления

этой проблемы большинство реально

использующихся схем виртуальной памяти

использует специальный кэш для записей

таблицы страниц, который обычно называют

буфером быстрого преобразования адреса

TLB. Этот кэш содержит те записи таблицы

страниц, которые использовались

последними.

Сегментная модель

оперативной памяти. Сегментация

позволяет рассматривать память как

область, состоящую из множества адресных

пространств, или сегментов. Сегменты

могут иметь динамические размеры.

Обращения к памяти используют адреса,

представляющие собой пары (номер

сегмента, смещение). Каждый процесс

имеет собственную таблицу сегментов,

и при загрузке всех сегментов процесса

в основную память создается таблица

сегментов процесса, которая также

загружается в основную память. В каждой

записи таблицы сегментов указан начальный

адрес соответствующего сегмента в

основной памяти и его длина. Та же таблица

сегментов нужна и при схеме виртуальной

памяти, основанной на сегментации.

Типичным приемом является использование

отдельной таблицы сегментов для каждого

процесса. Поскольку в основной памяти

могут находится, не все сегменты процесса,

в каждой записи требуется наличие бита

присутствия, указывающего, располагается

ли данный сегмент в основной памяти.

Если сегмент расположен в основной

памяти, то запись включает его начальный

адрес и длину. Еще один бит, необходимый

в данной схеме, — бит модификации,

указывающий, было ли изменено содержимое

сегмента со времени его последней

загрузки в основную память (рис.15).

Основной механизм

чтения слова из памяти включает

преобразование логического, адреса,

состоящего из номера сегмента и смещения,

в физический адрес с использованием

таблицы сегментов (рис.17). Когда запускается

определенный процесс, в регистре хранится

стартовый адрес его таблицы сегментов.

Номер сегмента из

виртуального адреса используется в

качестве индекса таблицы, позволяющего

определить начальный адрес сегмента.

Для получения физического адреса к

начальному адресу сегмента добавляется

смещение из виртуального адреса.

Рис. 17. Сегментная

организация памяти

Комбинация

сегментации и страничной организации

памяти.

Страничная

организация устраняет внешнюю фрагментацию

и обеспечивает эффективное использование

основной памяти. Поскольку перемещаемые

в основную память и из нее блоки имеют

фиксированный размер, облегчается

создание эффективных алгоритмов

управления памятью. Сегментация имеет

возможность обработки растущих структур

данных, поддержку совместного использования

и защиты памяти. В комбинированной

системе адресное пространство пользователя

разбивается на ряд сегментов по

усмотрению. Каждый сегмент в свою очередь

разбивается на ряд страниц фиксированного

размера, соответствующего размеру кадра

основной памяти. Если размер сегмента

меньше размера страницы, он занимает

страницу целиком. Логический адрес в

этом случае состоит из номера сегмента

и смещения в нем (рис.18).

Смещение в сегменте

следует рассматривать как номер страницы

определенного сегмента и смещение в

ней. С каждым процессом связана одна

таблица сегментов и несколько (по одной

на сегмент) таблиц страниц [3].

Рис. 18. Трансляция

адреса при сегментной и страничной

организации

При работе

определенного процесса в регистре

процессора хранится начальный адрес

соответствующей таблицы сегментов.

Получив виртуальный адрес, процессор

использует его часть, представляющую

номер сегмента, в качестве индекса в

таблице сегментов.

Соседние файлы в предмете [НЕСОРТИРОВАННОЕ]

- #

- #

- #

- #

- #

- #

- #

- #

- #

- #

- #

Одним из самых простых и эффективных способов повысить производительность персонального компьютера является увеличение объёма оперативной памяти. С годами операционные системы вроде Windows, тяжёлые приложения вроде Photoshop и браузеры такие как Chrome расходовали всё больше оперативной памяти.

Пару десятков лет назад компьютеры обходились объёмом памяти 2-4 Гб, но сейчас значения в 4 Гб хватит лишь для самых лёгких программ и точно не для браузера Chrome. Для современного компьютера минимально допустимым значением считается 8 Гб памяти, а оптимальным в данный момент 16 Гб. Разница в цене между 8 и 16 Гб не особо велика и многие могут себе позволить купить дополнительные планки. Если вы любитель компьютерных игр и хотите, чтобы ваш компьютер оставался современным как можно дольше, можно поставить 32 Гб. Конечно, это обойдётся заметно дороже.

На что обращать внимание при выборе оперативной памяти

Существуют разные типы памяти. Самые современные компьютеры используют память DDR4, более старые DDR3 или даже DDR2. В следующем году или через два года может быть представлена память DDR5.

Нужно обращать внимание не только на объём памяти, но и на её скорость. Судя по тестам, нет смысла покупать самую быструю память. Не стоит брать память с тактовой частотой 5 ГГц, каким бы красивым не выглядело это значение. Вместо этого лучше поискать оптимальное соотношение цены и производительности. В этом смысле лучшие планки памяти DDR4 обладают частотой в диапазоне 2666-3600 МГц. Выбирайте комплекты памяти с двумя модулями вместо одного, а ещё лучше с четырьмя.

HyperX Fury 32GB DDR4 3200MHz DIMM 288pin CL16 HX432C16FB3/32

Следует обратить внимание на производителя. Существует немало известных брендов, таких как Corsair, G.Skill, Kingston, KLEVV, Patriot, ADATA, Crucial, PNY, Super Talent, Mushkin. Главная разница между ними заключается в дизайне радиаторов охлаждения на модулях. Выбирайте память, где найдено лучшее сочетание внешнего вида и цены.

Споры относительно качества памяти от разных производителей могут вестись бесконечно, но в целом известные компании обычно не выпускают планки памяти низкого качества.

Как установить память в компьютер

Предположим, вы купили память объёмом 16 Гб. Пришла пора поставить её в системный блок. Этот процесс довольно быстрый и простой, если знать, что делать.

Сначала необходимо выключить компьютер и отсоединить его от розетки или нажать кнопку на блоке питания для его отключения. Дальше снимается боковая крышка системного блока, чтобы получить доступ к материнской плате.

Слоты оперативной памяти находятся поблизости от разъёма для процессора. Ищите крупный радиатор над материнской платой и рядом с ним наверняка будет два или четыре слота оперативной памяти.

Прежде чем устанавливать новые планки, необходимо извлечь старые. Нужно потянуть вбок пластиковые защёлки с обеих сторон слотов памяти, чтобы можно было вытащить модули.

Пока системный блок открыт, заодно можно почистить его от пыли при помощи пылесоса или баллона со сжатым воздухом.

Пора устанавливать планки памяти. Убедитесь, что вы ставите модули правильной стороной. Чтобы не ошибиться, на модуле памяти есть выемка, которая должна совпасть с перемычкой на слоте памяти. Если вы не заполните все доступные слоты памяти, читайте руководство материнской платы.

Некоторые модели предлагают устанавливать планки в другом порядке, вроде Slot 2 > Slot 4 > Slot 1 > Slot 3. Всё зависит от конкретной платы.

Впрочем, не стоит волноваться. Даже если вы установите планки в произвольном порядке, компьютер будет работать. Однако, вы можете лишиться многоканальной работы памяти и не получите максимальную производительность, если поставите планки не как надо.

Когда память установлена в слоты, закрепите её пластиковыми защёлками по бокам. Для этого нужно нажать на края памяти с двух сторон, пока не раздадутся щелчки.

Закройте системный блок, подключите все кабели, если отсоединяли их, включите блок питания и компьютер. Может потребоваться пара перезагрузок, прежде чем операционная система определит и настроит новую память. Обычно всё происходит с первого раза.

TrashExpert Staff

Над статьей работал не только один автор, но и другие члены команды TrashExpert: администратор, редакторы или коллектив авторов.

Введение

Мы продолжаем публикацию цикла «руководств пользователя», посвященных теоретическому и практическому рассмотрению различных компонентов современного ПК, начало которому положил материал «Современные десктопные процессоры архитектуры x86: общие принципы работы (x86 CPU FAQ 1.0)». В настоящем руководстве мы рассмотрим основные современные виды оперативной памяти, применяемой в десктопных системах (оперативную память, применяемую в серверах и ноутбуках, оставим за его рамками). Под ними будем подразумевать память класса SDRAM — SDR (Single Data Rate — память с одинарной скоростью передачи данных), DDR (Double Data Rate — память с удвоенной скоростью передачи данных) и DDR2 (память DDR второго поколения). Возможно, SDRAM «как таковая» (в ее первоначальном варианте SDR SDRAM) на сегодня уже не является столь актуальным видом памяти, тем не менее, все три перечисленных вида принадлежат одному и тому же классу и базируются примерно на одних и тех же принципах функционирования, которые мы и рассмотрим прямо сейчас.Содержание

- Часть 1. Теоретические основы современной оперативной памяти

- SDRAM: Определение

- Микросхемы SDRAM: Физическая организация и принцип работы

- Микросхемы SDRAM: Логическая организация

- Модули SDRAM: Организация

- Модули памяти: Микросхема SPD

- Тайминги памяти

- Схема доступа к данным микросхемы SDRAM

- Соотношения между таймингами

- Схемы таймингов

- Задержки командного интерфейса

- DDR/DDR2 SDRAM: Отличия от SDR SDRAM

Часть 1. Теоретические основы современной оперативной памяти

SDRAM: Определение

Аббревиатура SDRAM расшифровывается как Synchronous Dynamic Random Access Memory — синхронная динамическая память с произвольным доступом. Остановимся подробнее на каждом из этих определений. Под «синхронностью» обычно понимается строгая привязка управляющих сигналов и временных диаграмм функционирования памяти к частоте системной шины. Вообще говоря, в настоящее время изначальный смысл понятия синхронности становится несколько условным. Во-первых, частота шины памяти может отличаться от частоты системной шины (в качестве примера можно привести уже сравнительно давно существующий «асинхронный» режим работы памяти DDR SDRAM на платформах AMD K7 с чипсетами VIA KT333/400, в которых частоты системной шины процессора и шины памяти могут соотноситься как 133/166 или 166/200 МГц). Во-вторых, ныне существуют системы, в которых само понятие «системной шины» становится условным — речь идет о платформах класса AMD Athlon 64 с интегрированным в процессор контроллером памяти. Частота «системной шины» (под которой в данном случае понимается не шина HyperTransport для обмена данными с периферией, а непосредственно «шина» тактового генератора) в этих платформах является лишь опорной частотой, которую процессор умножает на заданный коэффициент для получения собственной частоты. При этом контроллер памяти всегда функционирует на той же частоте, что и сам процессор, а частота шины памяти задается целым делителем, который может не совпадать с первоначальным коэффициентом умножения частоты «системной шины». Так, например, режиму DDR-333 на процессоре AMD Athlon 64 3200+ будут соответствовать множитель частоты «системной шины» 10 (частота процессора и контроллера памяти 2000 МГц) и делитель частоты памяти 12 (частота шины памяти 166.7 МГц). Таким образом, под «синхронной» операцией SDRAM в настоящее время следует понимать строгую привязку временных интервалов отправки команд и данных по соответствующим интерфейсам устройства памяти к частоте шины памяти (проще говоря, все операции в ОЗУ совершаются строго по фронту/срезу синхросигнала интерфейса памяти). Так, отправка команд и чтение/запись данных может осуществляться на каждом такте шины памяти (по положительному перепаду — «фронту» синхросигнала; в случае памяти DDR/DDR2 передача данных происходит как по «фронту», так и по отрицательному перепаду — «срезу» синхросигнала), но не по произвольным временным интервалам (как это осуществлялось в асинхронной DRAM).

Понятие «динамической» памяти, DRAM, относится ко всем типам оперативной памяти, начиная с самой древней, «обычной» асинхронной динамической памяти и заканчивая современной DDR2. Этот термин вводится в противоположность понятия «статической» памяти (SRAM) и означает, что содержимое каждой ячейки памяти периодически необходимо обновлять (ввиду особенности ее конструкции, продиктованной экономическими соображениями). В то же время, статическая память, характеризующаяся более сложной и более дорогой конструкцией ячейки и применяемая в качестве кэш-памяти в процессорах (а ранее — и на материнских платах), свободна от циклов регенерации, т.к. в ее основе лежит не емкость (динамическая составляющая), а триггер (статическая составляющая).

Наконец, стоит также упомянуть о «памяти с произвольным доступом» — Random Access Memory, RAM. Традиционно, это понятие противопоставляется устройствам «памяти только на чтение» — Read-Only Memory, ROM. Тем не менее, противопоставление это не совсем верно, т.к. из него можно сделать вывод, что память типа ROM не является памятью с произвольным доступом. Это неверно, потому как доступ к устройствам ROM может осуществляться в произвольном, а не строго последовательном порядке. И на самом деле, наименование «RAM» изначально противопоставлялось ранним типам памяти, в которых операции чтения/записи могли осуществляться только в последовательном порядке. В связи с этим, более правильно назначение и принцип работы оперативной памяти отражает аббревиатура «RWM» (Read-Write Memory), которая, тем не менее, встречается намного реже. Заметим, что русскоязычным сокращениям RAM и ROM — ОЗУ (оперативное запоминающее устройство) и ПЗУ (постоянное запоминающее устройство), соответственно, подобная путаница не присуща.

Микросхемы SDRAM: Физическая организация и принцип работы

Общий принцип организации и функционирования микросхем динамической памяти (DRAM) практически един для всех ее типов — как первоначальной асинхронной, так и современной синхронной. Исключение составляют разве что экзотические варианты, тем не менее, существовавшие еще до появления SDRAM, вроде Direct Rambus DRAM (DRDRAM). Массив памяти DRAM можно рассматривать как матрицу (двумерный массив) элементов (строго говоря, это понятие относится к логическому уровню организации микросхемы памяти, рассмотренному в следующем разделе, но его необходимо ввести здесь для наглядности), каждый из которых содержит одну или несколько физических ячеек (в зависимости от конфигурации микросхемы), способных вмещать элементарную единицу информации — один бит данных. Ячейки представляют собой сочетание транзистора (ключа) и конденсатора (запоминающего элемента). Доступ к элементам матрицы осуществляется с помощью декодеров адреса строки и адреса столбца, которые управляются сигналами RAS# (сигнал выбора строки — Row Access Strobe) и CAS# (сигнал выбора столбца — Column Access Strobe).

Из соображений минимизации размера упаковки микросхемы, адреса строк и столбцов передаются по одним и тем же адресным линиям микросхемы — иными словами, говорят о мультиплексировании адресов строк и столбцов (упомянутые выше отличия в общих принципах функционирования микросхем DRDRAM от «обычных» синхронных/асинхронных DRAM проявляются, в частности, здесь — в этом типе микросхем памяти адреса строк и столбцов передаются по разным физическим интерфейсам). Так, например, 22-разрядный полный адрес ячейки может разделяться на два 11-разрядных адреса (строки и столбца), которые последовательно (через определенный интервал времени, см. раздел «Тайминги памяти») подаются на адресные линии микросхемы памяти. Одновременно со второй частью адреса (адреса столбца) по единому командно-адресному интерфейсу микросхемы SDRAM подается соответствующая команда (чтения или записи данных). Внутри микросхемы памяти адреса строки и столбца временно сохраняются в буферах (защелках) адреса строки и адреса столбца, соответственно.

Важно заметить, что с динамической матрицей памяти связан особый буфер статической природы, именуемый «усилителем уровня» (SenseAmp), размер которого равен размеру одной строки, необходимый для осуществления операций чтения и регенерации данных, содержащихся в ячейках памяти. Поскольку последние физически представляют собой конденсаторы, разряжающиеся при совершении каждой операции чтения, усилитель уровня обязан восстановить данные, хранящиеся в ячейке, после завершения цикла доступа (более подробно участие усилителя уровня в цикле чтения данных из микросхемы памяти рассмотрено ниже).

Кроме того, поскольку конденсаторы со временем теряют свой заряд (независимо от операций чтения), для предотвращения потери данных необходимо периодически обновлять содержимое ячеек. В современных типах памяти, которые поддерживают режимы автоматической регенерации (в «пробужденном» состоянии) и саморегенерации (в «спящем» состоянии), обычно это является задачей внутреннего контроллера регенерации, расположенного непосредственно в микросхеме памяти.

Схема обращения к ячейке памяти в самом общем случае может быть представлена следующим образом:

1. На адресные линии микросхемы памяти подается адрес строки. Наряду с этим подается сигнал RAS#, который помещает адрес в буфер (защелку) адреса строки.

2. После стабилизации сигнала RAS#, декодер адреса строки выбирает нужную строку, и ее содержимое перемещается в усилитель уровня (при этом логическое состояние строки массива инвертируется).

3. На адресные линии микросхемы памяти подается адрес столбца вместе с подачей сигнала CAS#, помещающего адрес в буфер (защелку) адреса столбца.

4. Поскольку сигнал CAS# также служит сигналом вывода данных, по мере его стабилизации усилитель уровня отправляет выбранные (соответствующие адресу столбца) данные в буфер вывода.

5. Сигналы CAS# и RAS# последовательно дезактивируются, что позволяет возобновить цикл доступа (по прошествии промежутка времени, в течение которого данные из усилителя уровня возвращаются обратно в массив ячеек строки, восстанавливая его прежнее логическое состояние).

Так выглядела реальная схема доступа к ячейке DRAM в самом первоначальном ее варианте, реализованном еще до появления первых реально используемых микросхем/модулей асинхронной памяти типа FPM (Fast Page Mode) DRAM. Тем не менее, нетрудно заметить, что эта схема является достаточно неоптимальной. Действительно, если нам требуется считать содержимое не одной, а сразу нескольких подряд расположенных ячеек, отличающихся только адресом столбца, но не адресом строки, то нет необходимости каждый раз подавать сигнал RAS# с одним и тем же адресом строки (т.е. выполнять шаги 1-2). Вместо этого, достаточно удерживать сигнал RAS# активным на протяжении промежутка времени, соответствующего, например, четырем последовательным циклам чтения (шаги 3-4, с последующей дезактивацией CAS#), после чего дезактивировать сигнал RAS#. Именно такая схема применялась в асинхронной памяти типа FPM DRAM и более поздней EDO (Enhanced Data Output) DRAM. Последняя отличалась опережающей подачей адреса следующего столбца, что позволяло достичь меньших задержек при операциях чтения.

В современных микросхемах SDRAM схема обращения к ячейкам памяти выглядит аналогично. Далее, в связи с обсуждением задержек при доступе в память (таймингов памяти), мы рассмотрим ее более подробно.

Микросхемы SDRAM: Логическая организация

А пока перейдем к рассмотрению организации микросхем памяти SDRAM на логическом уровне. Как уже было сказано выше, микросхема DRAM, фактически, представляет собой двумерный массив (матрицу) элементов, состоящих из одного или нескольких элементарных физических ячеек. Очевидно, что главной характеристикой этого массива является его емкость, выражаемая в количестве бит информации, которую он способен вместить. Часто можно встретить понятия «256-Мбит», «512-Мбит» микросхем памяти — речь здесь идет именно об этом параметре. Однако составить эту емкость можно разными способами — мы говорим сейчас не о количестве строк и столбцов, но о размерности, или «вместимости» индивидуального элемента. Последняя прямо связана с количеством линий данных, т.е. шириной внешней шины данных микросхемы памяти (но не обязательно с коэффициентом пропорциональности в единицу, что мы увидим ниже, при рассмотрении отличий памяти типа DDR и DDR2 SDRAM от «обычной» SDRAM). Ширина шины данных самых первых микросхем памяти составляла всего 1 бит, в настоящее же время наиболее часто встречаются 4-, 8- и 16- (реже — 32-) битные микросхемы памяти. Таким образом, микросхему памяти емкостью 512 Мбит можно составить, например, из 128М (134 217 728) 4-битных элементов, 64М (67 108 864) 8-битных элементов или 32М (33 554 432) 16-битных элементов — соответствующие конфигурации записываются как «128Mx4», «64Mx8» и «32Mx16». Первая из этих цифр именуется глубиной микросхемы памяти (безразмерная величина), вторая — шириной (выраженная в битах).

Существенная отличительная особенность микросхем SDRAM от микросхем более ранних типов DRAM заключается в разбиении массива данных на несколько логических банков (как минимум — 2, обычно — 4). Не следует путать это понятие с понятием «физического банка» (называемого также «ранком» (rank) памяти), определенным для модуля, но не микросхемы памяти — его мы рассмотрим далее. Сейчас лишь отметим, что внешняя шина данных каждого логического банка (в отличие от физического, который составляется из нескольких микросхем памяти для «заполнения» шины данных контроллера памяти) характеризуется той же разрядностью (шириной), что и разрядность (ширина) внешней шины данных микросхемы памяти в целом (x4, x8 или x16). Иными словами, логическое разделение массива микросхемы на банки осуществляется на уровне количества элементов в массиве, но не разрядности элементов. Таким образом, рассмотренные выше реальные примеры логической организации 512-Мбит микросхемы при ее «разбиении» на 4 банка могут быть записаны как 32Mx4x4 банка, 16Mx8x4 банка и 8Mx16x4 банка, соответственно. Тем не менее, намного чаще на маркировке микросхем памяти (либо ее расшифровке в технической документации) встречаются именно конфигурации «полной» емкости, без учета ее разделения на отдельные логические банки, тогда как подробное описание организации микросхемы (количество банков, строк и столбцов, ширину внешней шины данных банка) можно встретить лишь в подробной технической документации на данный вид микросхем SDRAM.

Разбиение массива памяти SDRAM на банки было введено, главным образом, из соображений производительности (точнее, минимизации системных задержек — т.е. задержек поступления данных в систему). В самом простом и пока достаточном изложении, можно сказать, что после осуществления любой операции со строкой памяти, после дезактивации сигнала RAS#, требуется определенное время для осуществления ее «подзарядки». И преимущество «многобанковых» микросхем SDRAM заключается в том, что можно обращаться к строке одного банка, пока строка другого банка находится на «подзарядке». Можно расположить данные в памяти и организовать к ним доступ таким образом, что далее будут запрашиваться данные из второго банка, уже «подзаряженного» и готового к работе. В этот момент вполне естественно «подзаряжать» первый банк, и так далее. Такая схема доступа к памяти называется «доступом с чередованием банков» (Bank Interleave).

Модули SDRAM: Организация

Основные параметры логической организации микросхем памяти — емкость, глубину и ширину, можно распространить и на модули памяти типа SDRAM. Понятие емкости (или объема) модуля очевидно — это максимальный объем информации, который данный модуль способен в себя вместить. Теоретически он может выражаться и в битах, однако общепринятой «потребительской» характеристикой модуля памяти является его объем (емкость), выраженный в байтах — точнее, учитывая современный уровень используемых объемов памяти — в мега-, или даже гигабайтах.

Ширина модуля — это разрядность его интерфейса шины данных, которая соответствует разрядности шины данных контроллера памяти и для всех современных типов контроллеров памяти SDRAM (SDR, DDR и DDR2) составляет 64 бита. Таким образом, все современные модули характеризуются шириной интерфейса шины данных «x64». Каким же образом достигается соответствие между 64-битная шириной шины данных контроллера памяти (64-битным интерфейсом модуля памяти), когда типичная ширина внешней шины данных микросхем памяти обычно составляет всего 4, 8 или 16 бит? Ответ очень прост — интерфейс шины данных модуля составляется простым последовательным «слиянием» внешних шин данных индивидуальных микросхем модуля памяти. Такое «заполнение» шины данных контроллера памяти принято называть составлением физического банка памяти. Таким образом, для составления одного физического банка 64-разрядного модуля памяти SDRAM необходимо и достаточно наличие 16 микросхем x4, 8 микросхем x8 (это наиболее часто встречаемый вариант) или 4 микросхем x16.

Оставшийся параметр — глубина модуля, являющийся характеристикой емкости (вместимости) модуля памяти, выраженной в количестве «слов» определенной ширины, вычисляется, как нетрудно догадаться, простым делением полного объема модуля (выраженного в битах) на его ширину (разрядность внешней шины данных, также выраженную в битах). Так, типичный 512-МБ модуль памяти SDR/DDR/DDR2 SDRAM имеет глубину, равную 512МБайт * 8 (бит/байт) / 64 бита = 64М. Соответственно, произведение ширины на глубину дает полную емкость модуля и определяет его организацию, или геометрию, которая в данном примере записывается в виде «64Мx64».

Возвращаясь к физическим банкам модуля памяти, заметим, что при использовании достаточно «широких» микросхем x8 или x16 ничего не мешает поместить и большее их количество, соответствующее не одному, а двум физическим банкам — 16 микросхем x8 или 8 микросхем x16. Так различают однобанковые (или «одноранковые», single-rank) и двухбанковые («двухранковые», dual-rank) модули. Двухбанковые модули памяти наиболее часто представлены конфигурацией «16 микросхем x8», при этом один из физических банков (первые 8 микросхем) расположен с лицевой стороны модуля, а второй из них (оставшиеся 8 микросхем) — с тыльной. Наличие более одного физического банка в модуле памяти нельзя считать определенным преимуществом, т.к. может потребовать увеличения задержек командного интерфейса, которые рассмотрены в соответствующем разделе.

Модули памяти: Микросхема SPD

Еще до появления первого типа синхронной динамической оперативной памяти SDR SDRAM стандартом JEDEC предусматривается, что на каждом модуле памяти должна присутствовать небольшая специализированная микросхема ПЗУ, именуемая микросхемой «последовательного обнаружения присутствия» (Serial Presence Detect, SPD). Эта микросхема содержит основную информацию о типе и конфигурации модуля, временных задержках (таймингах, см. следующий раздел), которых необходимо придерживаться при выполнении той или иной операции на уровне микросхем памяти, а также прочую информацию, включающую в себя код производителя модуля, его серийный номер, дату изготовления и т.п. Последняя ревизия стандарта SPD модулей памяти DDR2 также включает в себя данные о температурном режиме функционирования модулей, которая может использоваться, например, для поддержания оптимального температурного режима посредством управления синхронизацией (регулированием скважности импульсов синхросигнала) памяти (так называемый «троттлинг памяти», DRAM Throttle). Более подробную информацию о микросхеме SPD и о том, как выглядит ее содержимое можно получить в нашей статье «SPD — схема последовательного детектирования», а также в серии наших исследований модулей оперативной памяти.

Тайминги памяти

Немаловажной категорией характеристик микросхем/модулей памяти являются «тайминги памяти» — понятие, наверняка так или иначе знакомое каждому пользователю ПК. Понятие «таймингов» тесно связано с задержками, возникающими при любых операциях с содержимым ячеек памяти в связи со вполне конечной скоростью функционирования устройств SDRAM, как и любых других интегральных схем. Задержки, возникающие при доступе в память, также принято называть «латентностью» памяти (этот термин не совсем корректен, и пришел в обиход с буквальным переводом термина latency, означающего «задержка»).

В этом разделе мы рассмотрим, где именно возникают задержки при операциях с данными — содержимым микросхем памяти, и как они связаны с важнейшими параметрами таймингов памяти. Поскольку в настоящем руководстве мы рассматриваем модули памяти класса SDRAM (SDR, DDR и DDR2), ниже мы рассмотрим конкретную схему доступа к данным, содержащимся в ячейках памяти микросхемы SDRAM. В этом разделе мы также рассмотрим несколько иную категорию таймингов, связанных не с доступом к данным, но с выбором номера физического банка для маршрутизации команд по командному интерфейсу модулей памяти класса SDRAM — так называемые «задержки командного интерфейса».

Схема доступа к данным микросхемы SDRAM

1. Активизация строки

Перед осуществлением любой операции с данными, содержащимися в определенном банке микросхемы SDRAM (чтения — команда READ, или записи — команда WRITE), необходимо «активизировать» соответствующую строку в соответствующем банке. С этой целью, на микросхему подается команда активизации (ACTIVATE) вместе с номером банка (линии BA0-BA1 для 4-банковой микросхемы) и адресом строки (адресные линии A0-A12, реальное количество которых зависит от количества строк в банке, в рассматриваемом примере 512-Мбит микросхемы памяти SDRAM их число составляет 213 = 8192).

Активизированная строка остается открытой (доступной) для последующих операций доступа до поступления команды подзарядки банка (PRECHARGE), по сути, закрывающей данную строку. Минимальный период «активности» строки — от момента ее активации до момента поступления команды подзарядки, определяется минимальным временем активности строки (Row Active Time, tRAS).

Повторная активизация какой-либо другой строки того же банка не может быть осуществлена до тех пор, пока предыдущая строка этого банка остается открытой (т.к. усилитель уровня, содержащий буфер данных размером в одну строку банка и описанный в разделе «Микросхемы SDRAM: Физическая организация и принцип работы», является общим для всех строк данного банка микросхемы SDRAM). Таким образом, минимальный промежуток времени между активизацией двух различных строк одного и того же банка определяется минимальным временем цикла строки (Row Cycle Time, tRC).

В то же время, после активизации определенной строки определенного банка микросхеме SDRAM ничего не мешает активизировать какую-либо другую строку другого банка (в этом и заключается рассмотренное выше преимущество «многобанковой» структуры микросхем SDRAM) на следующем такте шины памяти. Тем не менее, в реальных условиях производителями устройств SDRAM обычно здесь также умышленно вводится дополнительная задержка, именуемая «задержкой от активации строки до активации строки» (Row-to-Row Delay, tRRD). Причины введения этой задержки не связаны с функционированием микросхем памяти как таковых и являются чисто электрическими — операция активизации строки потребляет весьма значительное количество электрического тока, в связи с чем частое их осуществление может приводить к нежелательным избыточным нагрузкам устройства по току.

2. Чтение/запись данных

Следующий временной параметр функционирования устройств памяти возникает в связи с тем, что активизация строки памяти сама по себе требует определенного времени. В связи с этим, последующие (после ACTIVATE) команды чтения (READ) или записи (WRITE) данных не могут быть поданы на следующем такте шины памяти, а лишь спустя определенный временной интервал, называемый «задержкой между подачей адреса строки и столбца» (RAS#-to-CAS# Delay, tRCD).

Итак, после прошествия интервала времени, равного tRCD, при чтении данных в микросхему памяти подается команда READ вместе с номером банка (предварительно активизированного командой ACTIVATE) и адресом столбца. Устройства памяти типа SDRAM ориентированы на чтение и запись данных в пакетном (Burst) режиме. Это означает, что подача всего одной команды READ (WRITE) приведет к считыванию из ячеек (записыванию в ячейки) не одного, а сразу нескольких подряд расположенных элементов, или «слов» данных (разрядность каждого из которых равна ширине внешней шины данных микросхемы — например, 8 бит). Количество элементов данных, считываемых одной командой READ или записываемых одной командой WRITE, называется «длиной пакета» (Burst Length) и обычно составляет 2, 4 или 8 элементов (за исключением экзотического случая передачи целой строки (страницы) — «Full-Page Burst», когда необходимо дополнительно использовать специальную команду BURST TERMINATE для прерывания сверхдлинной пакетной передачи данных). Заметим, что для микросхем памяти типа DDR и DDR2 параметр Burst Length не может принимать значение меньше 2 и 4 элементов, соответственно — причину этого мы рассмотрим ниже, в связи с обсуждением различий в реализации устройств памяти SDR/DDR/DDR2 SDRAM.

Возвращаясь к чтению данных, заметим, что существует две разновидности команды чтения. Первая из них является «обычным» чтением (READ), вторая называется «чтением с автоматической подзарядкой» (Read with Auto-Precharge, «RD+AP»). Последняя отличается тем, что после завершения пакетной передачи данных по шине данных микросхемы автоматически будет подана команда подзарядки строки (PRECHARGE), тогда как в первом случае выбранная строка микросхемы памяти останется «открытой» для осуществления дальнейших операций.

После подачи команды READ, первая порция данных оказывается доступной не сразу, а с задержкой в несколько тактов шины памяти, в течение которой данные, считанные из усилителя уровня, синхронизируются и передаются на внешние выводы микросхемы. Задержка между подачей команды чтения и фактическим «появлением» данных на шине считается наиболее важной и именуется пресловутой «задержкой сигнала CAS#» (CAS# Latency, tCL). Последующие порции данных (в соответствии с длиной передаваемого пакета) оказываются доступными без каких-либо дополнительных задержек, на каждом последующем такте шины памяти (по 1 элементу за такт для устройств SDR, по 2 элемента в случае устройств DDR/DDR2).

Операции записи данных осуществляются аналогичным образом. Точно также существуют две разновидности команд записи — простая запись данных (WRITE) и запись с последующей автоматической подзарядкой строки (Write with Auto-Precharge, «WR+AP»). Точно также при подаче команды WRITE/WR+AP на микросхему памяти подаются номер банка и адрес столбца. Наконец, точно также запись данных осуществляется «пакетным» образом. Отличия операции записи от операции чтения следующие. Во-первых, первую порцию данных, подлежащих записи, необходимо подать по шине данных одновременно с подачей по адресной шине команды WRITE/WR+AP, номера банка и адреса столбца, а последующие порции, количество которых определяется длиной пакета — на каждом последующем такте шины памяти. Во-вторых, вместо «задержки сигнала CAS#» (tCL) важной здесь является иная характеристика, именуемая «периодом восстановления после записи» (Write Recovery Time, tWR). Эта величина определяет минимальный промежуток времени между приемом последней порции данных, подлежащих записи, и готовности строки памяти к ее закрытию с помощью команды PRECHARGE. Если вместо закрытия строки требуется последующее считывание данных из той же самой открытой строки, то приобретает важность другая задержка, именуемая «задержкой между операциями записи и чтения» (Write-to-Read Delay, tWTR).

3. Подзарядка строки

Цикл чтения/записи данных в строки памяти, который в общем случае можно обозначить «циклом доступа к строке памяти», завершается закрытием открытой строки банка с помощью команды подзарядки строки — PRECHARGE (которая, как мы уже отмечали выше, может быть «автоматической», т.е. являться составной частью команд «RD+AP» или «WR+AP»). Последующий доступ к этому банку микросхемы становится возможным не сразу, а по прошествию интервала времени, называемого «временем подзарядки строки» (Row Precharge Time, tRP). За этот период времени осуществляется собственно операция «подзарядки», т.е. возвращения элементов данных, соответствующих всем столбцам данной строки с усилителя уровня обратно в ячейки строки памяти.

Соотношения между таймингами

В заключение этой части, посвященной задержкам при доступе к данным, рассмотрим основные соотношения между важнейшими параметрами таймингов на примере более простых операций чтения данных. Как мы рассмотрели выше, в самом простейшем и самом общем случае — для пакетного считывания заданного количества данных (2, 4 или 8 элементов) необходимо осуществить следующие операции:

1) активизировать строку в банке памяти с помощью команды ACTIVATE;

2) подать команду чтения данных READ;

3) считать данные, поступающие на внешнюю шину данных микросхемы;

4) закрыть строку с помощью команды подзарядки строки PRECHARGE (как вариант, это делается автоматически, если на втором шаге использовать команду «RD+AP»).

Временной промежуток между первой и второй операцией составляет «задержку между RAS# и CAS#» (tRCD), между второй и третьей — «задержку CAS#» (tCL). Промежуток времени между третьей и четвертой операциями зависит от длины передаваемого пакета. Строго говоря, в тактах шины памяти он равен длине передаваемого пакета (2, 4 или 8), поделенного на количество элементов данных, передаваемых по внешней шине за один ее такт — 1 для устройств типа SDR, 2 для устройств типа DDR. Условно назовем эту величину «tBL».

Важно заметить, что микросхемы SDRAM позволяют осуществлять третью и четвертую операции в некотором смысле «параллельно». Чтобы быть точным — команду подзарядки строки PRECHARGE можно подавать за некоторое количество тактов x до наступления того момента, на котором происходит выдача последнего элемента данных запрашиваемого пакета, не опасаясь при этом возникновения ситуации «обрыва» передаваемого пакета (последняя возникнет, если команду PRECHARGE подать после команды READ с временным промежутком, меньшим x). Не вдаваясь в подробности, отметим, что этот промежуток времени составляет величину, равную величине задержки сигнала CAS# за вычетом единицы (x = tCL — 1).

Наконец, промежуток времени между четвертой операцией и последующим повтором первой операции цикла составляет «время подзарядки строки» (tRP).

В то же время, минимальному времени активности строки (от подачи команды ACTIVATE до подачи команды PRECHARGE, tRAS), по его определению, как раз отвечает промежуток времени между началом первой и началом четвертой операции. Отсюда вытекает первое важное соотношение между таймингами памяти:

tRAS, min = tRCD + tCL + (tBL — (tCL — 1)) — 1,

где tRCD — время выполнения первой операции, tCL — второй, (tBL — (tCL — 1)) — третьей, наконец, вычитание единицы производится вследствие того, что период tRAS не включает в себя такт, на котором осуществляется подача команды PRECHARGE. Сокращая это выражение, получаем:

tRAS, min = tRCD + tBL.

Достаточно поразительный вывод, вытекающий из детального рассмотрения схемы доступа к данным, содержащимся в памяти типа SDRAM, заключается в том, что минимальное значение tRAS не зависит(!) от величины задержки CAS#, tCL. Зависимость первого от последнего — достаточно распространенное заблуждение, довольно часто встречающееся в различных руководствах по оперативной памяти.